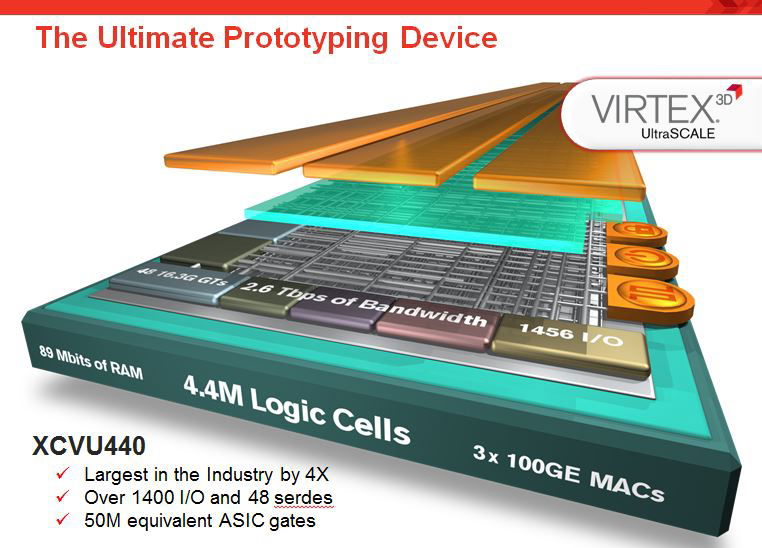

Ce circuit offre une capacité équivalant à celle d’un Asic de 50 millions de portes.

Xilinx vient de démarrer la livraison du FPGA Virtex UltraScale VU440, un modèle dont la capacité équivaut à celle d’un circuit spécifique de 50 millions de portes logiques, soit quatre fois plus que le concurrent le plus proche selon l’américain.

Il utilise pour cela la seconde génération de technologie d’assemblage multipuce SSI de Xilinx, basée sur le procédé CoWoS (Chip-on-Wafer-on-Substrate) du fondeur taiwanais TSMC.

Le VU440 embarque 4,4 millions de blocs logiques, 1456 entrées-sorties disponibles pour l’utilisateur, 89 Mbits de Ram et 48 ports 16,3 Gbit/s.