Le japonais développe une mémoire flash Nand à 96 couches de cellules TLC (3 bits par cellules), ainsi qu’un modèle à 64 couches de cellules QLC (4 bits par cellules).

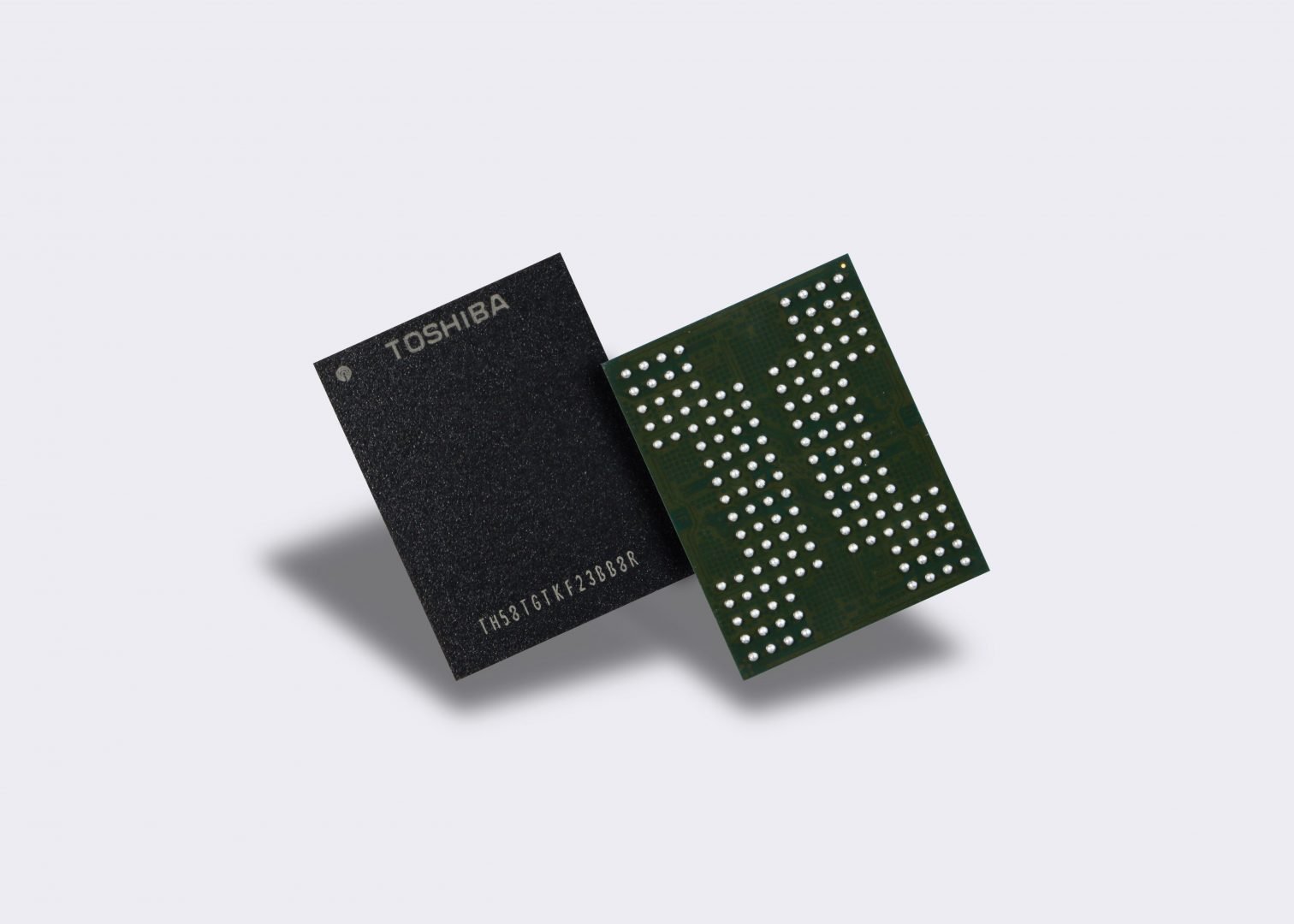

Toshiba Memory a développé un prototype de mémoire flash Nand à empilement vertical comprenant pas moins de 96 couches. Rappelons que l’état de l’art pour ces mémoires dites V-Nand chez Samsung et BiCS chez Toshiba est actuellement de 64 couches de cellules empilées. Le prototype de Toshiba utilise des cellules à 3 bits et comprend en tout 32Go de données. Les premiers échantillons devraient être disponibles au second semestre 2017, avec production en volume en 2018. Ces puces seront fabriquées sur le site de Yokkaichi dans les Fab 2 et 5 et dans la nouvelle Fab 6 qui ouvrira en été 2018.

Dans le même temps, Toshiba Memory a annoncé le développement d’une mémoire flahs Nand BiCS à 64 couches exploitant cette fois des cellules à 4 bits. Le premier prototype embarque ainsi 96Go de données sur une seule puce. Cette technologie permettra également au japonais de lancer des modules miniatures à 16 puces offrant une capacité de 1,5To.