L’américain abaisse de 20 % la latence de son architecture PCIe 4.0 et de 15 % la surface de silicium requise.

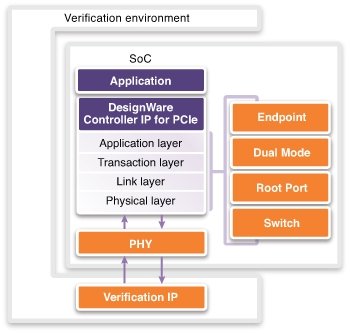

Synopsys a optimisé son architecture d’interface PHY et de contrôleur PCIe 4.0 afin d’en augmenter les performances. Disponible sous forme d’IP au sein du catalogue DesignWare de l’américain, cette architecture présente désormais une latence en baisse de 20% et utilise 15% de surface de silicium en moins. Les débits de données varient de 2,5 à 16GT/s, en technologie 65nm à 10nm.