Le japonais a développé une structure de mémoire Sram ternaire spécifique capable d’accélérer les réseaux neuronaux à convolution en effectuant les opérations MAC en interne.

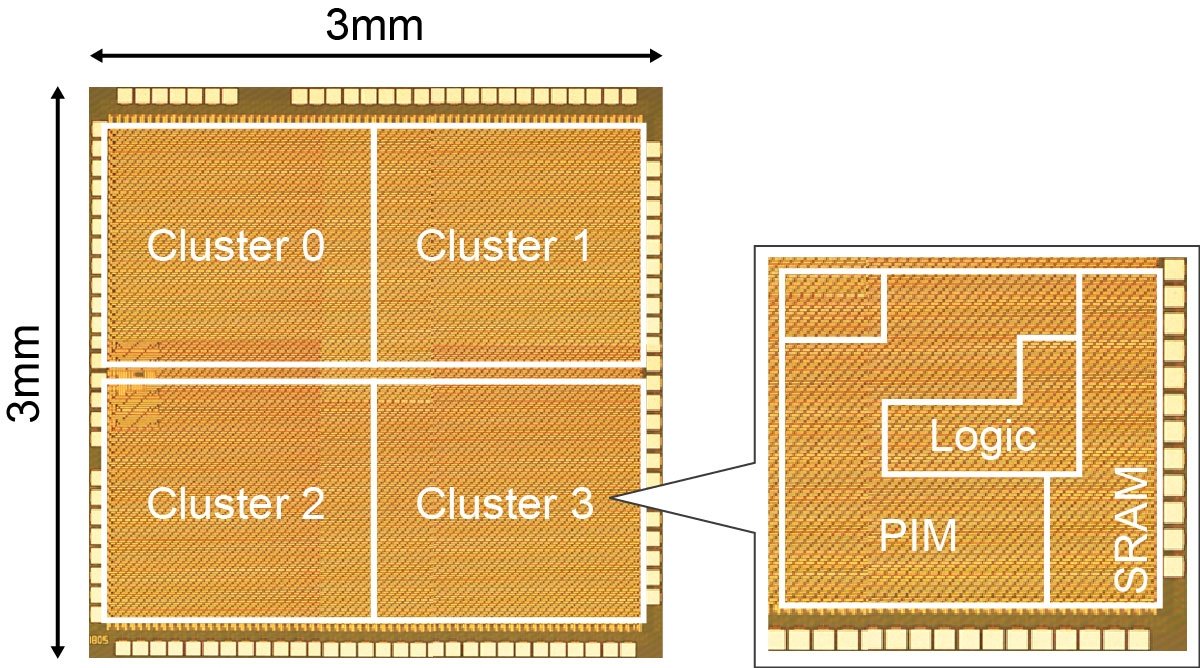

Renesas Electronics profite de la conférence VLSI Technology and Circuits, qui se déroule actuellement à Kyoto, pour dévoiler un accélérateur de réseaux neuronaux à convolution exécuté au niveau de la mémoire. Le prototype de circuit exposé développe une puissance de calcul de 8,8 Tops/W, à l’état de l’art actuel selon le japonais. Les opérations de multiplication et d’accumulation nécessaires au traitement CNN sont ici effectuées dans la mémoire, à mesure que les données en sont extraites, grâce à une structure de cellule Sram ternaire, des comparateurs à basse consommation situés en sortie de ces cellules Sram et une technologie de production évitant les erreurs de calcul induites par les variations de process.