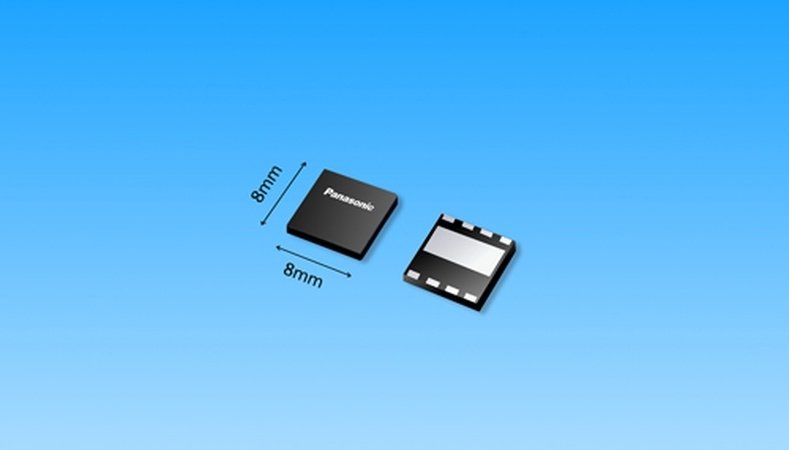

Le japonais va lancer des transistors à enrichissement de 600V, en GaN sur silicium, dont l’empreinte sur la carte est de 8x8mm seulement.

Panasonic compte échantillonner en juillet des transistors de puissance en GaN sur substrat silicium, dont la particularité est liée à leurs faibles dimensions. Ces transistors, dont la tension de claquage est de 600V, seront en effet encapsulés dans un boîtier DFN de 8x8x1,25mm seulement. Ce qui, vis-à-vis d’un format TO-220 conventionnel, se traduit par une réduction de l’empreinte de 43%. L’adoption d’un boîtier CMS a aussi pour effet de réduire les inductances parasites, pour garantir une vitesse de commutation de 200V/ns.

Ces transistors à enrichissement, normalement bloqués, adoptent le principe d’injection de grille, dit GIT (Gate Injection Transistor), du japonais. Les premiers modèles seront les PGA26E19BV de 10A et PGA26E08BV de 15A. Sont notamment en ligne de mire : les alimentations AC-DC, les systèmes de charge de batterie, les onduleurs photovoltaïques…