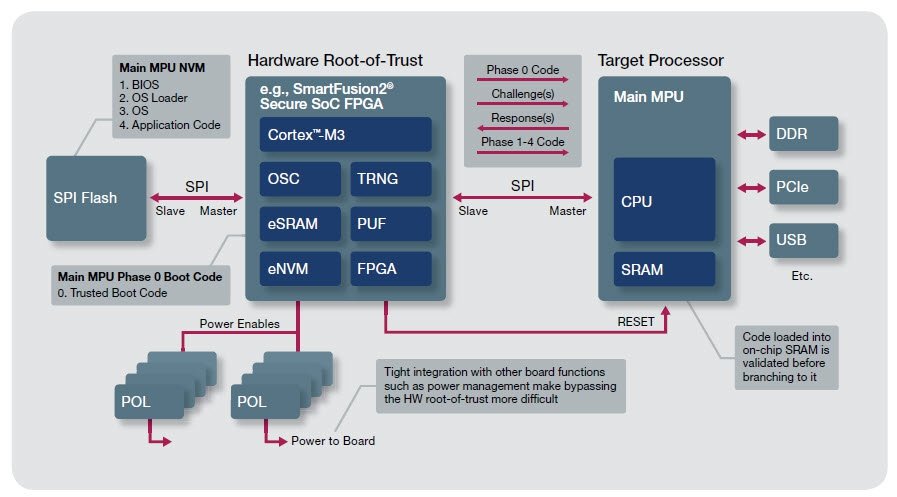

L’américain utilise ses FPGA SmartFusion 2 pour sécuriser chaque étape d’initialisation d’un processeur embarqué.

Microsemi lance une solution basée sur ses FPGA SmartFusion 2 et permettant de sécuriser l’initialisation de systèmes architecturés autour d’un processeur embarqué. Cette conception de référence assure que chaque étape d’initialisation du processeur soit validée par le code précédemment authentifié avant que la suite du code ne soit exécutée. Les SmartFusion 2 embarque pour cela un stockage de clés, un générateur de nombres aléatoires non déterministe, un stockage du code d’initialisation en flash sécurisée ou encore une émulation en temps réel de la flash via une interface SPI, avec des mesures de protection DPA contre les intrusions licenciées auprès de Cryptography Research. Outre cette conception de référence générique, Microsemi s’apprête également à lancer des versions dédiées aux processeurs ARM, Intel ou encore Freescale.