L’américain a conçu une interface PAM4 à 56 Gbit/s sur ses FPGA en technologie FinFET 16 nm produits par TSMC.

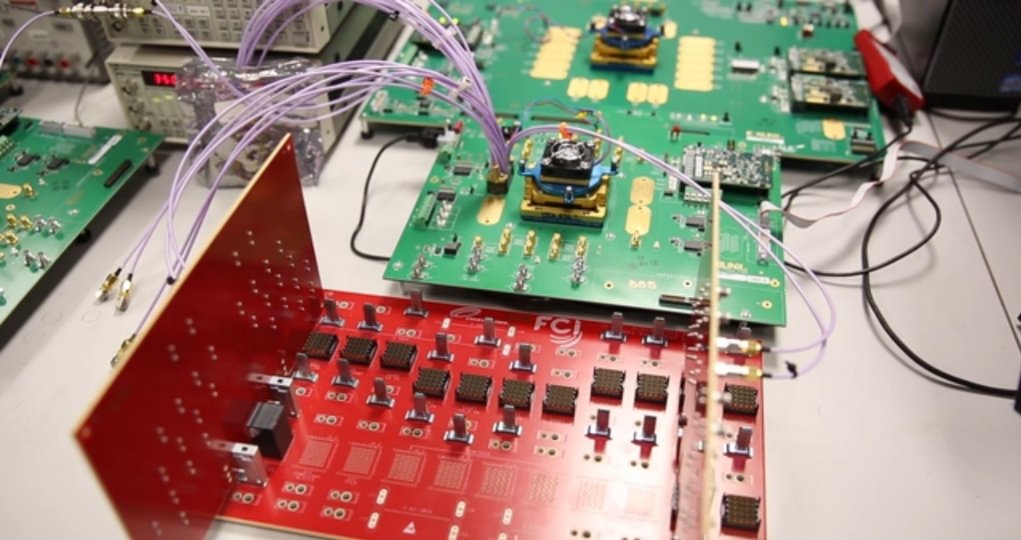

Xilinx a développé un bloc d’émission-réception PAM4 à 56Gbit/s sur l’un de ses FPGA en technoogie FinFET 16nm. L’américain exhibera cette technologie lors du salon OFC qui se tiendra à Anaheim du 22 au 24 mars prochain. Développée en collaboration avec TSMC, elle supporte des liaisons de type cuivre et optique, et ouvre la voie à des fonds de panier au-delà des 400Gbit/s et à des cartes de lignes dépassant la barre du Tbit/s.