L’américain lance une IP de vérification pour interface haut débit PCI Express 6.0 et achève le développement des IP de contrôle et de couche physique ad hoc.

La prochaine déclinaison de l’interface haut débit PCI Express est dans les starting-blocks. Synopsys achève actuellement une solution PCIe 6.0 complète, la première de l’industrie selon l’américain. Cette plateforme comprend les IP de contrôle, de couche physique (PHY) et de vérification, permettant d’intégrer des interfaces PCIe 6.0 dans un circuit numérique. Elle supporte les dernières fonctions ajoutées à la spécification, y compris la signalisation PAM-4 à 64GT/s, le mode FLIT et le mode de consommation L0p.

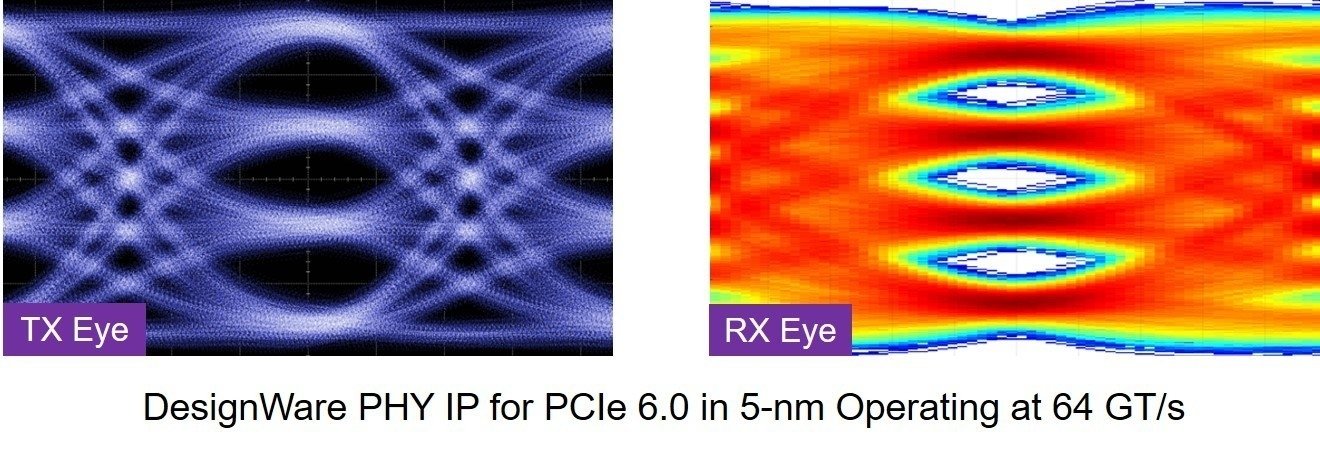

La partie contrôle repose sur une architecture 1024 bits pouvant atteindre 64GT/s sur 16 canaux avec une fréquence de travail de 1GHz. La partie PHY bénéficie, elle, d’algorithmes DSP spécifiques qui optimisent l’égalisation analogique et numérique des signaux pour améliorer le rendement. Parmi les applications visées figurent les serveurs cloud, le stockage de données et l’apprentissage automatique, avant que la technologie PCIe 6.0 ne se popularise à terme jusqu’aux PC grand public. L’IP de vérification PCIe 6.0 est d’ores et déjà disponibles, celles correspondant au contrôleur et au bloc PHY le seront au troisième trimestre 2021.