L’organisme Semi a interviewé plusieurs experts de ce domaine qui feront des présentations à Semicon West (San Francisco, du 12 au 14 juillet 2016).

La lithographie aux UV extrêmes est attendue depuis longtemps. Aujourd’hui, son introduction en production est envisagée pour le nœud technologique 5nm. L’organisme Semi a interviewé des experts du domaine qui s’exprimeront sur ce sujet lors de Semicon West (San Francisco, du 12 au 14 juillet 2016). Voici un résumé de ce qu’a écrit Semi.

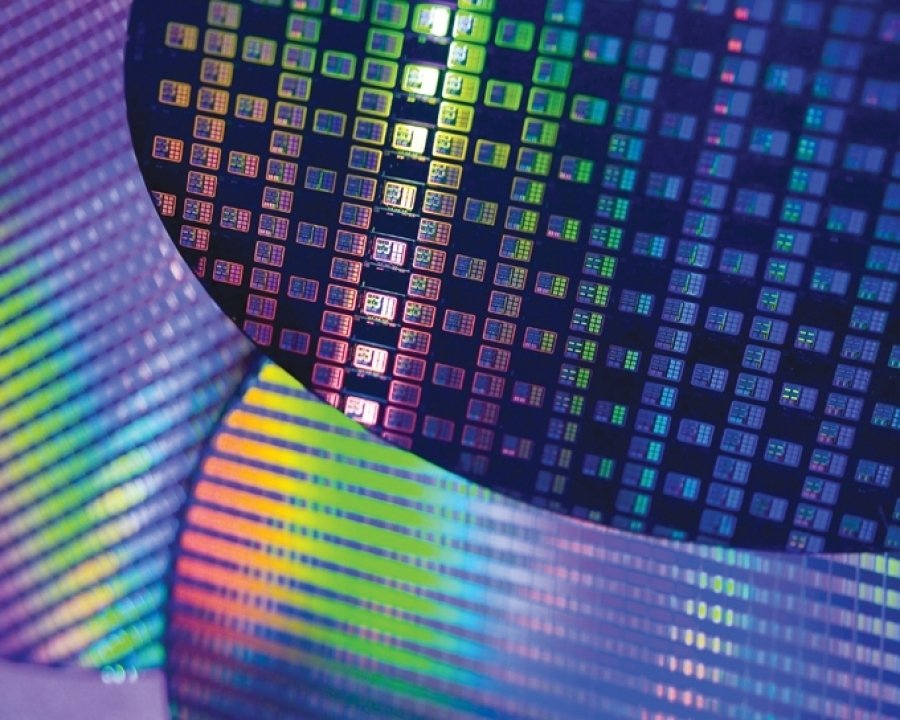

Mike Lercel, directeur du marketing produits d’ASML, a indiqué que sa société a récemment montré que l’équipement de lithographie aux UV extrêmes NXE :3300B, équipé d’une source de puissance supérieure à 80W, a permis l’exposition de 1368 wafers en 24 heures (57w/h) de bonne qualité. Or, les experts estiment que la lithographie EUV serait rentable si elle permet l’obtention de 1500 wafers de bonne qualité par jour.

Reste qu’ASML doit encore augmenter la puissance de la source d’énergie UV : M. Lercel a d’ailleurs annoncé qu’une source de 125W est prête à l’emploi, qu’une source de 200W est en voie de qualification et qu’une source de 250W devrait être annoncée par ASML d’ici à la fin de l’année. « 250W, c’est la puissance requise en production pour 1500 wafers par jour », a-t-il indiqué.

Au plan du timing, Mike Lercel estime que l’introduction de la lithographie EUV pour les circuits logiques se fera au niveau du 5nm, en 2018 ou 2019.

L’EUV : un bouleversement

TSMC a annoncé qu’il prévoit d’utiliser la lithographie EUV en parallèle à la lithographie optique 193nm en immersion avec multiple patterning (scission des motifs à reproduire en sous-motifs) pour la fabrication des circuits intégrés en largeur de trait 7nm.

Le numéro 1 mondial de la fonderie de silicium envisage l’utilisation en production de la lithographie EUV pour le 5nm. « A condition que la litho EUV soit au point en 2018-2019 », remarque Chris Mack, spécialiste mondial de la lithographie EUV.

En outre, M. Mack rappelle qu’un fondeur met environ deux ans pour passer de l’utilisation de nouvelles règles de design – comme c’est le cas avec l’EUV – à la production de circuits intégrés réalisés à partir de ces nouvelles règles.

Le coût de production pose aussi problème : « le fait de suivre la loi de Moore est légitimé par le fait que la miniaturisation continue du transistor de base va de pair avec une diminution du coût de celui-ci », rappelle Chris Mack. Or, cette diminution de coût dans le cas du passage au 7nm puis au 5nm n’est pas si évidente que cela. « S’il n’y a pas diminution de coût, les raisons de passer aux nœuds en-deçà de 10nm seront moins évidentes », remarque M. Mack.

Semi mentionne également les problèmes à résoudre concernant les outils d’inspection des masques vierges et des masques recouvert d’un film de protection, ainsi que les travaux sur les nouvelles résines chimiquement amplifiées (CAR pour Chemically Amplified Resist).