L’américain a généreusement augmenté la quantité de mémoire cache Sram et Dram embarquée dans ses processeurs multicoeurs pour centres de données informatiques.

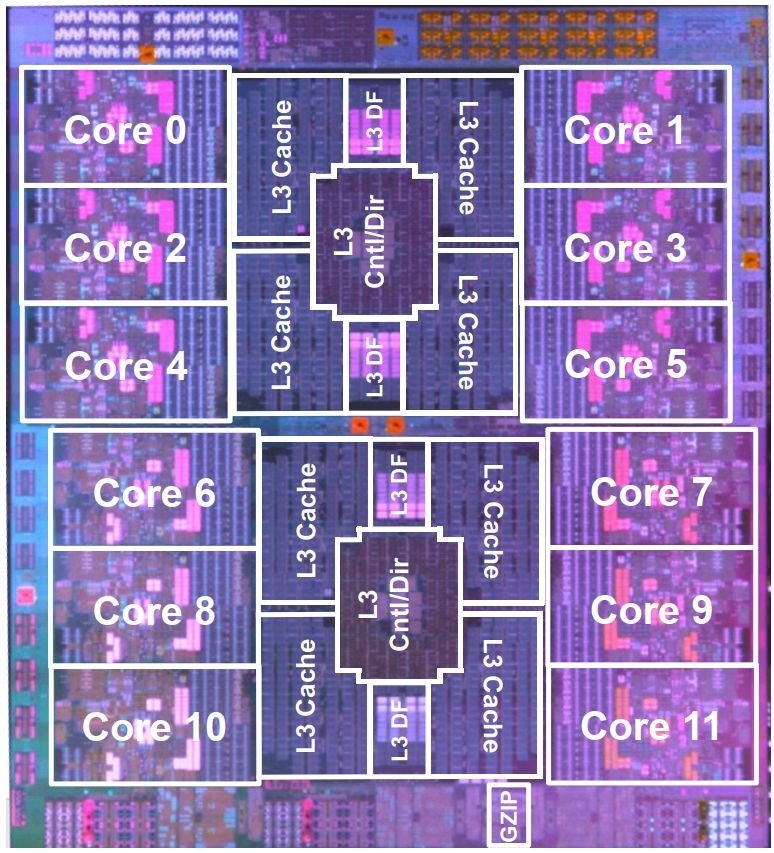

San Francisco – IBM profite de la conférence ISSCC, dont l’édition 2020 se tient actuellement à San Francisco, pour détailler ses tous derniers microprocesseurs équipant ses systèmes informatiques z15. Ces processeurs sont fabriqués en technologie 14nm FinFET sur SOI par GlobalFoundries. Mesurant 696mm², chaque processeur central (CP) intègre 12 coeurs cadencés jusqu’à 5,2GHz, 256Mo de Dram pour la mémoire cache de niveau 3, trois interfaces PCIe Gen4, deux interfaces X-BUS pour la connexion à un autre CP et à un contrôleur système (SC) et une interface vers le réseau de mémoires externes. Chacun des 12 coeurs dispose, lui, de 8Mo de cache Dram de niveau 2 et de 256Ko de cache Sram de niveau 1 – des tailles de cache sensiblement augmentées par rapport au z14.

La nouvelle topologie associe un SC et quatre CP (soit 240 coeurs physiques au total) sur des cartes 19″ standard. Si les CP comprennent 9,2 milliards de transistors, les SC montent, eux, à 12,2 milliards de transistors, notamment en raison des 960Mo de cache Dram de niveau 4 embarqués. Toute cette mémoire aide à soutenir les améliorations fonctionnelles apportées au z15, dans les domaines de la prédiction d’embranchement, du traitement multitâche, de l’exécution dans le désordre, du cryptage ECC ou encore de la compression zEDC. IBM a également mis en oeuvre une surveillance proactive des baisses de tension, qui permet au processeur de réagir 48 cycles plus tôt en cas de problème d’alimentation.