Grâce à un étage d’entrée sophistiqué et une correction numérique intensive, l’américain repousse les limites de ses convertisseurs A/N haut débit destinés à l’échantillonnage de signaux RF.

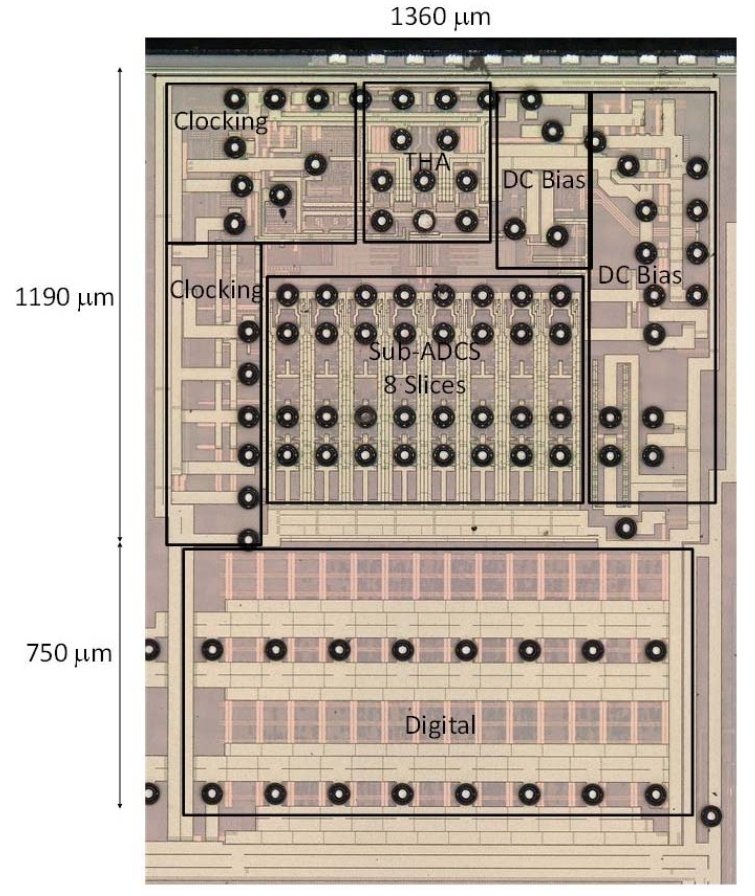

San Francisco – Analog Devices a présenté à la conférence ISSCC un CAN 12 bits délivrant pas moins de 18Géch./s (l’état de l’art se situant plutôt à 10Géch./s à cette résolution), et principalement destiné à l’échantillonnage de signaux RF. Analog Devices a choisi d’utiliser, en lieu et place du buffer d’entrée classique, un bloc d’amplification track-and-hold (THA) pilotant huit moteurs de conversion analogique-numérique à pipeline afin de limiter les problèmes d’échantillonnage RF et la valeur de la capacitance d’entrée. En faisant porter une partie du travail sur les épaules de ce THA, l’architecture d’Analog Devices permet d’utiliser des sous-CAN pipeline relativement rapides et économiques car implémentables dans un process à géométrie fine, ici du FinFET 16nm. La puce finale occupe 2,6mm² de silicium (un bon tiers étant dévolu aux nombreux blocs de calibration et de compensation numériques), consomme 1,3W à plein régime avec une bande passante d’entrée de 18GHz, un plancher de bruit de -157dBFS/Hz et une marge dynamique SFDR de 56dB à 4GHz et 54dB à 8GHz.