ARM a développé un prototype de microcontrôleur 32 bits Cortex-M33 à mémoires Rom et Ram consommant moins de 4 mW en mode actif et 10 nW en veille.

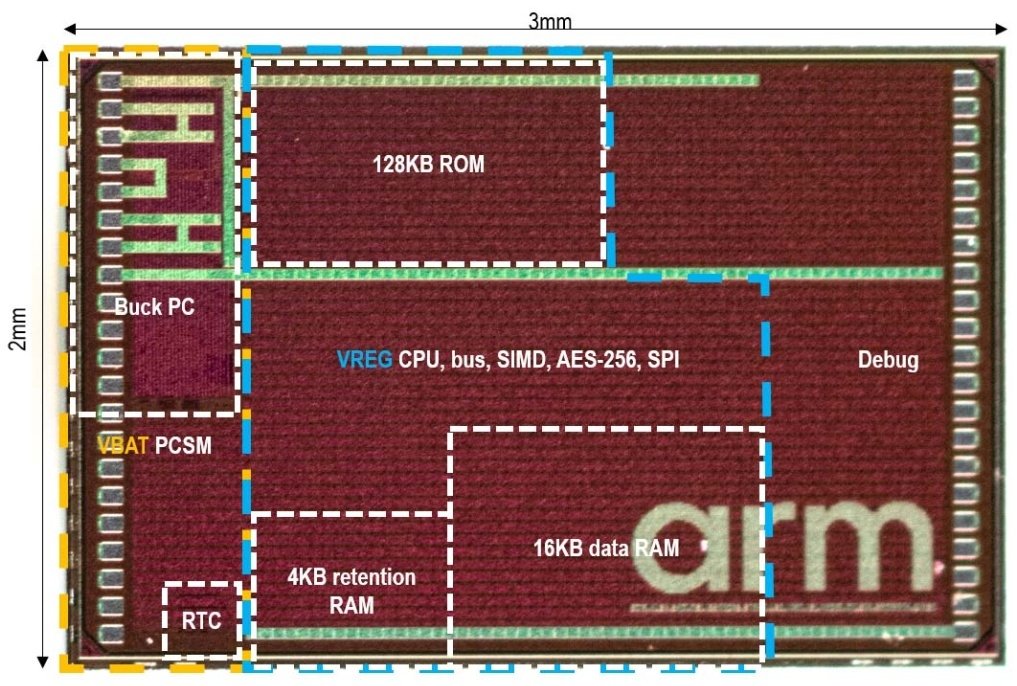

San Francisco – ARM a présenté lors de la conférence ISSCC M0N0, une architecture de microcontrôleur à très faible consommation qui convient par exemple aux capteurs déployés sur site et qui a été cofinancée par la Darpa américaine. Fabriqué en technologie Cmos 65 nm, le prototype M0N0 repose sur un cœur Cortex-M33 bénéficiant d’une adaptation dynamique de tension et de fréquence ou DVFS (dynamic voltage and frequency scaling). Concrètement, la tension d’alimentation principale, comprise entre 1V et 1,5V, est appliquée à un convertisseur abaisseur de tension, une machine d’états gérant les modes veille et l’horloge temps réel. Le reste de la puce – cœur Cortex-M33, mémoires Rom et Ram, moteur de cryptage AES-256, interface SPI – est alimenté sous 0,4V à 0,75V, la fréquence maximale du cœur variant alors entre 0,8MHz et 38MHz. En mode actif, la consommation de l’ensemble varie entre 5µW et 4mW. Celle-ci chute à seulement 10nW en veille.