Le sud-coréen poursuit ses développements en mémoires flash Nand à empilement dotées de cellules stockant quatre bits.

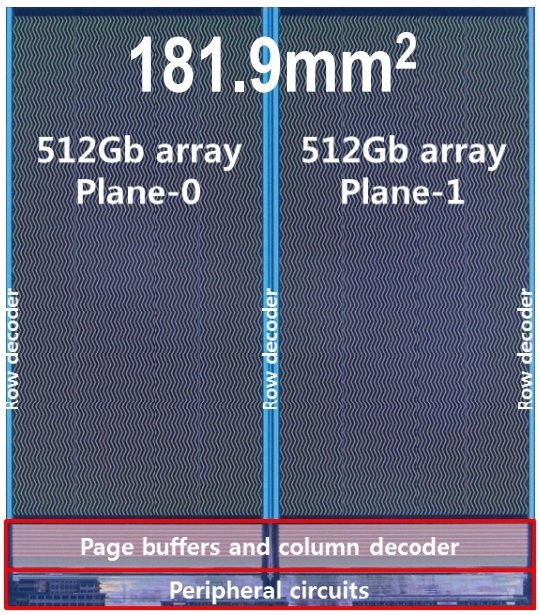

San Francisco – Samsung a exposé lors de la conférence ISSCC une mémoire flash Nand à 64 couches dotées de cellules à quatre bits (QLC) pour une capacité totale de 1Tbits et une densité de 5,63Gbit/mm². Si il permet de compenser un nombre de couches Nand inférieur, le stockage de quatre bits par cellule apporte son lot de problèmes. Le nombre d’états étant multiplié par deux, la programmation de la cellule devient plus ardue et sa fiabilité plus sujette à caution.

Samsung a mis en œuvre plusieurs techniques pour pallier ces défis. Parmi elles, on retiendra une méthode de reprogrammation ayant pour effet de « nettoyer » les cellules mémoires pour compenser les facteurs de dégradation usuels tels que la perte de charge initiale (par migration latérale, effet tunnel vertical et recombinaison) et l’interférence entre lignes de cellules. Cette technique a pour effet de diminuer le taux d’erreurs binaires de 84% selon le sud-coréen. Un mécanisme de seconde lecture rapide (fast read retry) vise, lui, à s’affranchir des dérives de la tension de transfert au cours de la vie de la mémoire, et améliore donc sa longévité.