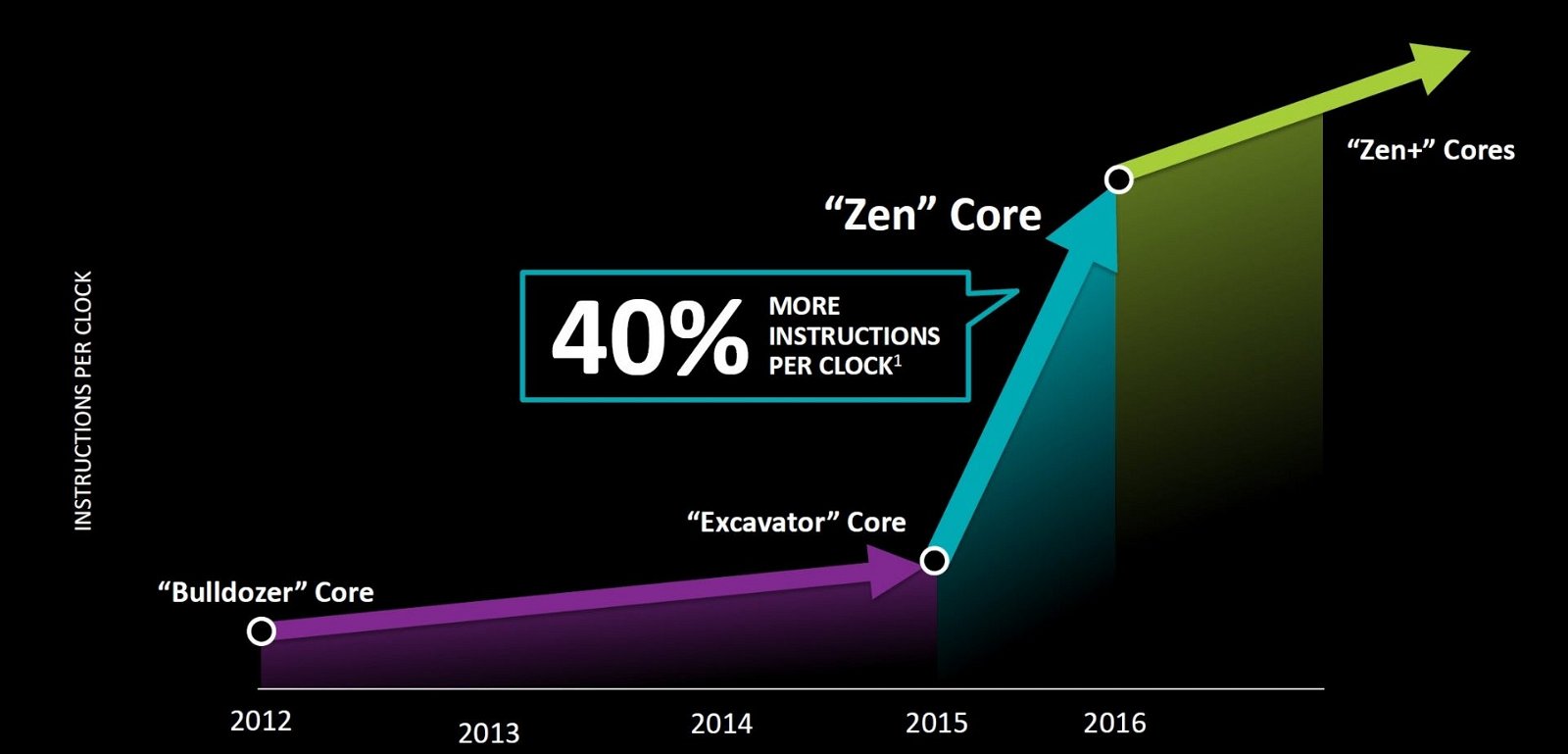

L’américain annonce une augmentation de 40 % du nombre d’instructions traitées par cycle d’horloge par rapport à la précédente architecture Excavator.

San Francisco – Dans le cadre de la conférence ISSCC, AMD a levé le voile sur le cœur Zen qui servira désormais de moteur unique à ses processeurs x86, qu’ils visent les systèmes à basse consommation (ordinateurs portables et clients fanless) ou les ordinateurs haut de gamme. Ce cœur est regroupé par paquets de quatre au sein d’une unité dite CCX qui, avec ses 8Mo de mémoire cache de niveau 3, occupe 44mm² pour 1,4 milliard de transistors dans la technologie FinFET 14nm LPP de Globalfoundries. Chaque cœur Zen occupe, lui, 7mm² avec ses 32+64Ko de cache de niveau 1 (données + instructions) et 512Ko de cache L2, sans oublier un régulateur à faible chute de tension et un synthétiseur de fréquence numérique (digital frequency synthesizer ou DFS) par cœur afin d’en moduler la cadence selon la charge de travail.

Créée à partir d’une feuille blanche, l’architecture Zen traite 40% d’instructions en plus par cycle d’horloge que la précédente Excavator et devient multitâche, gérant huit tâches actives par bloc CCX. Zen ajoute également un cache stockant les instructions décodées, ce qui accélère encore la puce tout en réduisant sa consommation en raccourcissant la pipeline. Par rapport à la génération précédente, la latence de la mémoire cache L3 a été réduite de 30%, grâce à une optimisation de son organisation et aux synthétiseurs DFS capables d’insérer des décalages de l’ordre de 15% du cycle d’horloge.