Samsung a développé une cellule Sram mesurant seulement 0,04 µm² en technologie FinFET 10 nm.

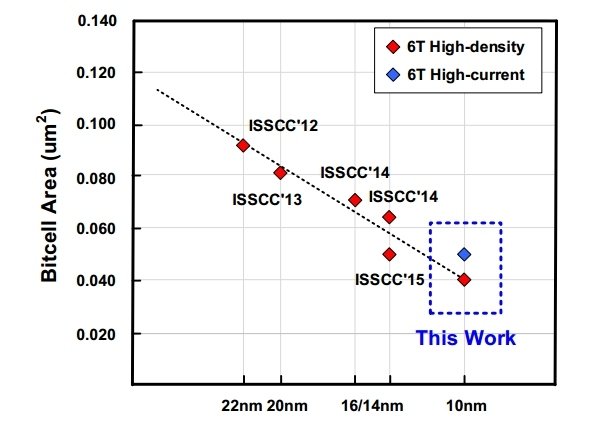

San Francisco – Samsung a présenté lors d’ISSCC la plus petite cellule Sram fabriquée à ce jour. Le sud-coréen a utilisé une technologie FinFET 10nm pour obtenir une cellule Sram à six transistors mesurant 0,04µm² dans sa version haute densité et 0,049µm² pour le modèle rapide à fort courant – un gain de 38% par rapport aux travaux existants en technologie FinFET 14nm. Au total, la puce de démonstration de Samsung embarque 128Mbits de Sram dans une surface de 75,6mm².

Mais il ne suffit pas de recourir à une géométrie de fabrication plus avancée pour réduire la taille des cellules Sram. En effet, plus les technologies s’affinent et plus les variations de process font sentir leurs effets sur la tension de fonctionnement minimale à laquelle la mémoire fonctionne à plein régime sans erreur. Pour déterminer la pertinence des différentes fonctions d’assistance couramment utilisées pour améliorer les performances, le fabricant a étudié leurs effets précis sur les deux types de cellules. Cette étude l’a amené à choisir une ligne de mot à double transition ou DTWL (dual-transcient word line) pour les cellules rapides, car moins pénalisante au niveau du timing que le recours à une ligne de bit négative ou NBL (negative bit line) tout en abaissant la tension de fonctionnement de 45mV. Pour les cellules à haute densité, Samsung a opté pour une combinaison de NBL et de SBL (suppressed bit line, qui permet d’abaisser le bruit en lecture) : la tension de fonctionnement a ainsi pu être diminuée de 130mV.