Des universitaires japonais ont optimisé la circulation des données en fonction des spécificité du codage HEVC pour concevoir une puce de décodage 7680x4320p à 120 images par seconde.

San Francisco - L’Université de Waseda (Japon) a présenté à ISSCC la première solution monocircuit de décodage vidéo 8K (7680x4320) H.265/HEVC 8/10bits de l’industrie. Avec un débit de données brut 80 fois supérieure à celui du 1080p et une complexité de traitement par pixel près de 4 fois supérieure en raison de la compression nécessairement apportée par le codage HEVC, la tâche n’est pas aisée. La circulation des données entre les différents moteurs de traitement est dévolue soit à des Fifo classiques, soit à des queues de type Bibo (block-in block-out), dans lesquelles des blocs de données, de taille variable et susceptibles d’être réunis ou au contraire coupés en morceaux si besoin est, sont stockés comme dans une Fifo tout en permettant l’accès aléatoire à des mots de données au sein d’un bloc. Les pipelines de données entre unités de traitement sont synchronisés en fonction de ces queues Fifo et Bibo et non pas par l’intermédiaire d’un séquençage général de la puce, ce qui fluidifie la circulation des données quelles que soit leur granularité.

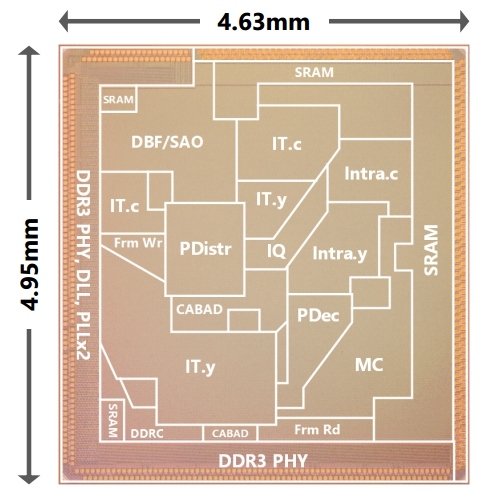

Cette organisation permet d’éliminer de nombreux registres tampons (buffers) et d’obtenir une utilisation typique de pipeline de 83,3% malgré les entêtes imposés par la Dram, très sollicitée car les blocs regroupent jusqu’à 64x64 pixels contre 16x16 en H.264. Cette organisation interne, qui colle au plus près du fonctionnement du codage HEVC, permet à la puce de 4,95x4,63mm en Cmos 40nm de manipuler jusqu’à 4Gpixel/s, correspondant à un flux 7680x4320p à 120 images par seconde. A plein régime, le décodeur est cadencé à 300 MHz et la Dram à 660 MHz, pour une consommation (hors Dram) de 690 mW.