Samsung et Toshiba continuent de plancher sur les MRam pour en améliorer la célérité et en diminuer la consommation.

San Francisco – Les MRam ont cette année les honneurs de la conférence ISSCC, en particulier leur déclinaison STT-MRam (Spin Transfer Torque magnetoresistive Ram), avec deux papiers à l’honneur. Le premier, œuvre de Samsung, propose une solution à l’un des problèmes freinant encore le fonctionnement de ces mémoires MRam, à savoir les variations erratiques de la jonction tunnel et la faible magnétorésistance liée.

La solution de Samung réside dans des amplificateurs de mesure à architecture BCSA (covalent-bonded sense amplifier) évitant le recours à une topologie de mesure différentielle qui réduit la densité de la puce mémoire.

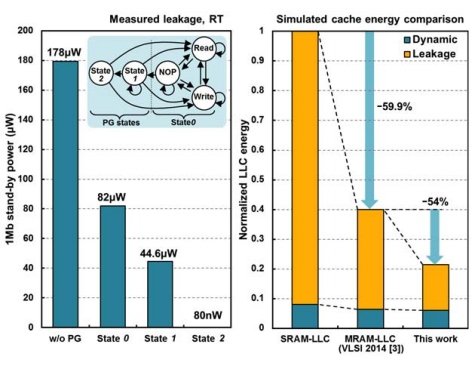

L’autre publication sur les STT-MRAM, signée Toshiba, s’attache surtout à accélérer leur débit de données tout en diminuant leur consommation. Le prototype 1Mbits en Cmos 65nm du japonais offre un temps d’accès en lecture de seulement 3,3ns sous 1,2V.

La consommation, elle, est réduite à 44,6µW en veille et 80nW en veille profonde, ce dernier mode étant obtenu par une gestion affinée du power gating et n’induisant qu’une latence de 21ns.