L’américain échantillonnera au troisième trimestre une toute nouvelle famille de circuits logiques programmables, des modèles FinFET 10 nm modulaires, rapides et optimisés pour fonctionner avec les processeurs Xeon.

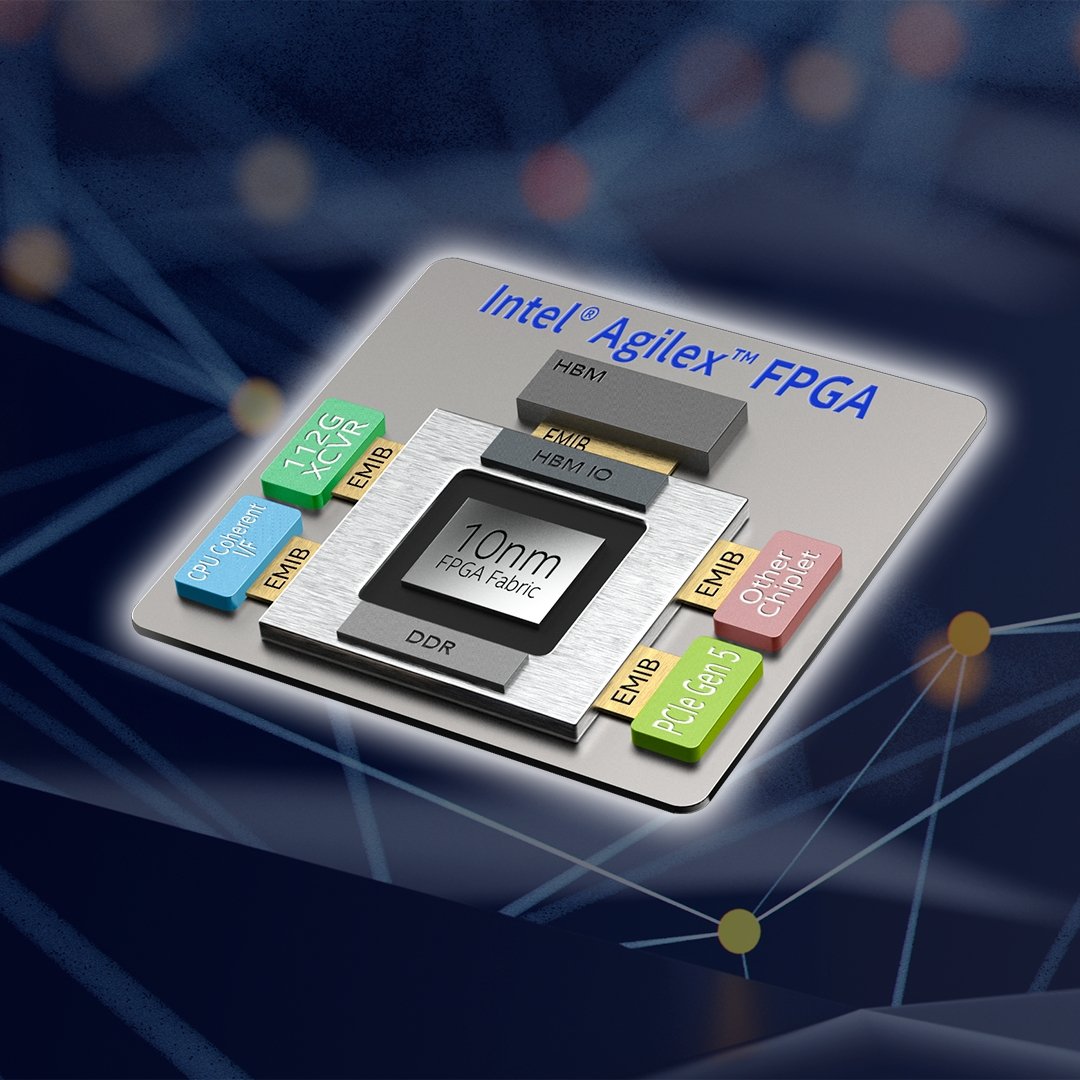

Intel va échantillonner une nouvelle famille de FPGA baptisée Agilex. Ces circuits logiques programmables fabriqués en technologie FinFET 10nm sont assemblés dans des modules 3D avec d’autres briques de base (chiplets), notamment de la mémoire, fabriquées en technologie 10, 14 ou 22 nm selon les besoins de la fonction. Côté performances, Intel annonce un gain de 40% à consommation égale par rapport aux Stratix 10 actuels. Les Agilex sont aussi les premiers FPGA supportant l’interface Compute Express Link qui fournit une connexion directe et cohérente, tant au niveau de la mémoire générale que de la mémoire cache, avec les processeurs Xeon. Les blocs DSP embarqués génèrent jusqu’à 40Tflops de puissance de calcul. Les Agilex comprennent également des ports PCIe Gen 5, des blocs d’émission-réception culminant à 112Gbit/s et des interfaces mémoires compatibles avec les mémoires DDR5, HBM et Optane DC. Trois gammes sont envisagées, par ordre croissant de puissance : les Agilex F (transmetteurs 58Gbit/s, PCIe 4, DDR4), les Agilex I (transmetteurs 112Gbit/s, PCIe 5, DDR4, interface Xeon) et les Agilex M (transmetteurs 112Gbit/s, PCIe 5, DDR4/5 et Optane, interface Xeon, option HBM). Les premiers circuits devraient être disponibles au troisième trimestre 2019, avec un support dans l’environnement de développement Quartus d’ores et déjà actif.