L'américain et ses partenaires de recherche planchent sur un process de fabrication de puces en 5 nm à partir d'une structure de transistors GaaFET original.

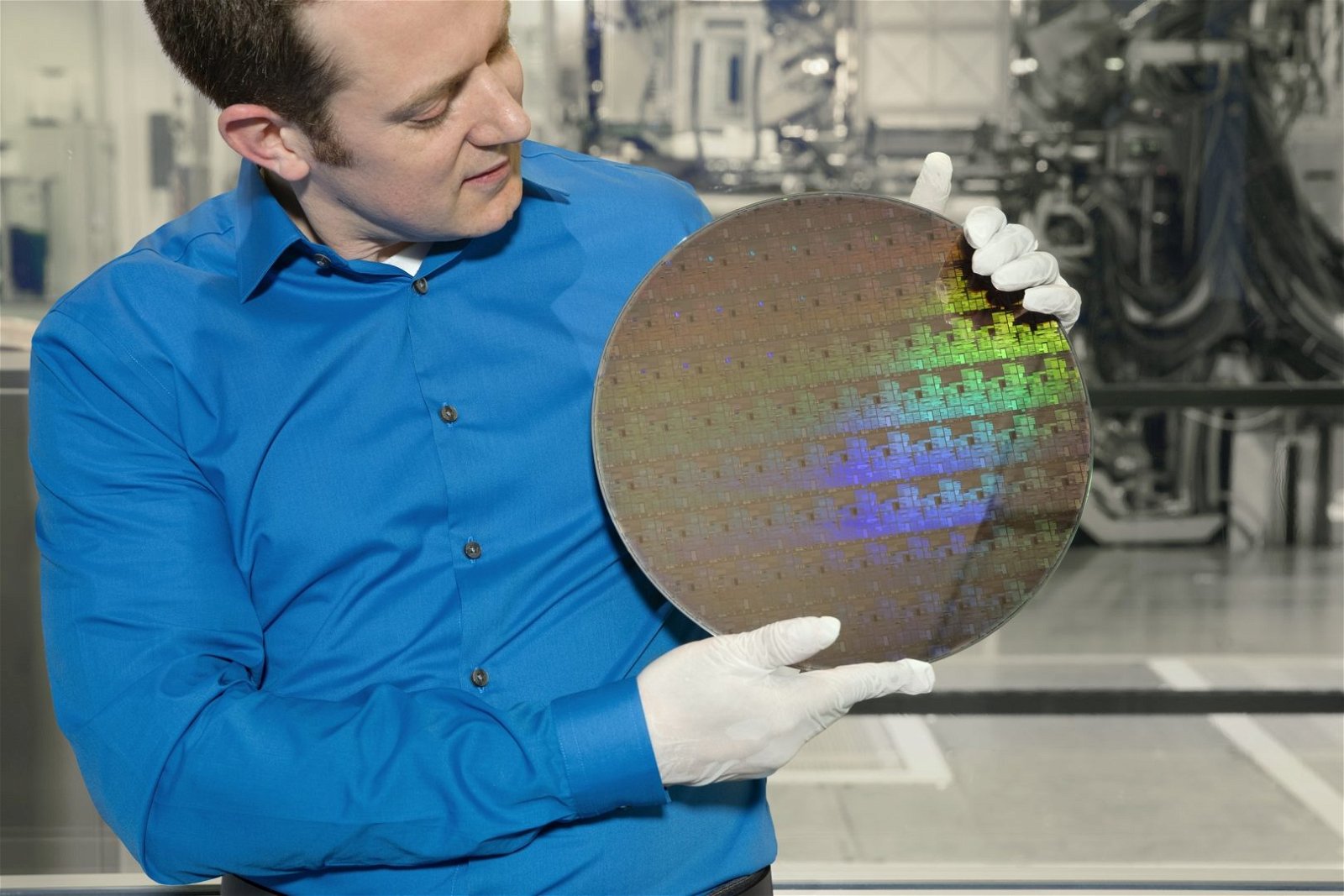

IBM, ses partenaires Globalfoundries et Samsung et leurs fournisseurs d'équipements ont développé le premier process permettant de fabriquer des transistors pour puces en géométrie 5nm.

Ces transistors présentent non pas une architecture FinFET comme ceux utilisés jusqu'en 7nm, mais sont de type GaaFET (gate-all-around FET) nanosheets. Il sont constitués comme leur nom l'indique d'une grille entourant complètement le canal de conduction des électrons (alors que dans un FinFET, elle n'en contrôle que trois côtés), ce canal étant composé ici de trois nanofeuilles de silicium dont on peut optimiser les performances en jouant sur la largeur.

D'après IBM, cette technologie 5nm devrait offrir un gain de 40% en performance à consommation égale ou de 75% en consommation à performance égale par rapport à un process 10nm actuel.