Altera lève le voile sur les blocs d’émission-réception 32 Gbit/s destinés à ses prochains FPGA en technologie 20 nm. Altera vient de lever le voile sur les blocs d’émission-réception 32 Gbit/s appelés à équiper ses prochains FPGA en technologie 20 nm. Ces blocs offrent une gigue totale de 9 ps et une gigue aléatoire de 240 fs – de quoi répondre aux exigences des systèmes 100 Gbit/s. Pour la génération 28 nm actuelle, les blocs d’émission-réception d’Altera sont limités à 28 Gbit/s.

Dans la même rubrique

Le 07/01/2022 à 11:01 par Christelle Erémian

Les ventes mondiales de semi-conducteurs devraient atteindre 680Md$ en 2022

D’après le cabinet d’études IC Insights, les ventes de semi-conducteurs devraient augmenter de 11% en 2022 pour atteindre 680,6Md$. Un…

Le 04/11/2021 à 10:29 par Christelle Erémian

Les livraisons de semi-conducteurs atteignent des records au troisième trimestre 2021

Alors que la pénurie de composants perdure, jamais autant de puces n'auront été livrées au cours de l'histoire du marché…

Le 13/09/2021 à 8:46 par Frédéric Rémond

Pluie de microcontrôleurs Cortex-M4 200MHz chez Toshiba

Le Japonais étoffe sa gamme TXZ+ de microcontrôleurs 32 bits haut de gamme d'une vingtaine de modèles. Toshiba ajoute vingt…

Le 13/09/2021 à 8:23 par Frédéric Rémond

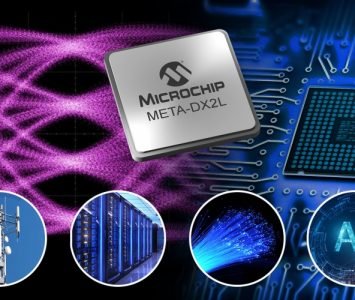

Les circuits Ethernet PHY adoptent les ports à 112Gbit/s

Microchip développe un circuit Ethernet PHY compact, à faible consommation et gérant jusqu'à 1,6Tbit/s. L'explosion des débits de…