La quatrième génération de l’architecture DSP CEVA-XC délivre jusqu’à 150 % de performances supplémentaires pour les infrastructures télécoms et réseaux.

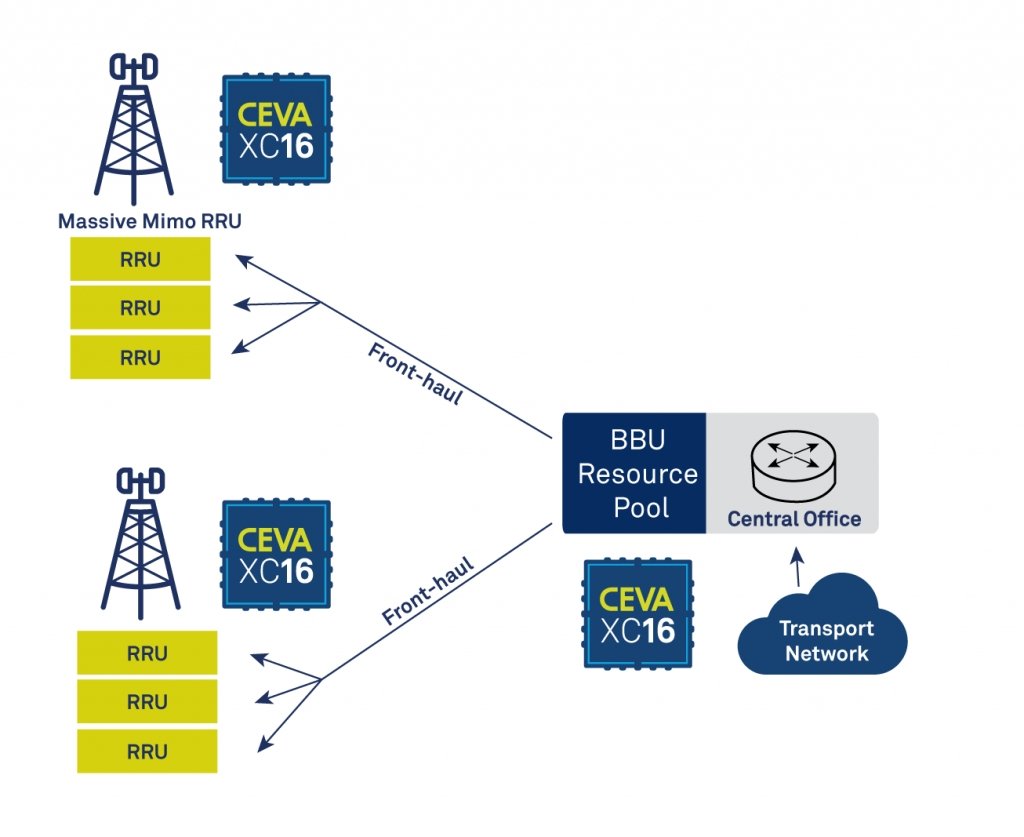

Avec sa quatrième génération de DSP CEVA-XC, l’américain cible les applications les plus exigeantes telles que les réseaux haut débit et les infrastructures télécoms. Basés sur une architecture à pipeline profond et des instructions VLIW, les DSP CEVA-XC Gen4 sont cadencés jusqu’à 1,8GHz en technologie FinFET 7nm. Ils bénéficient également d’un nouveau sous-système mémoire dont la bande passante atteint 2048 bits, d’instructions supplémentaires pour les algorithmes FFT et FIR et d’unités de traitement vectoriel remaniées. Premier processeur exploitant cette architecture, le CEVA-XC16 délivre jusqu’à 1600Gops susceptibles d’être répartis sur deux tâches parallèles distinctes. Il sera disponible au deuxième trimestre 2020.