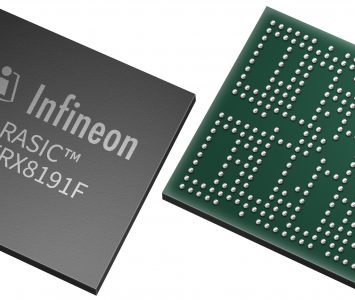

L’Américain fait monter en gamme ses circuits logiques programmables fabriqués sur process FD-SOI avec des modèles comptant jusqu’à 100K cellules logiques et acceptant les mémoires LPDDR4.

Les circuits logiques programmables à architecture Nexus de Lattice Semiconductor gagnent en densité. Les CertusPro-NX intègrent jusqu’à 100K cellules logiques, huit lignes Serdes programmables délivrant 10,3Gbit/s, 7,3Mbits de mémoire, 156 multiplicateurs 18×18 et des interfaces Dram LPDDR4, PCIe, Ethernet 10Gbit/s, SLVS-EC, CoaXPress et DisplayPort. Encapsulés dans des boîtiers aussi compacts que 9x9mm, ces FPGA n’entendent pas concurrencer les modèles Xilinx ou Intel dans les “grosses” applications, mais se destinent aux systèmes embarqués en tant que coprocesseurs, passerelles haut débit, interfaces pour capteurs, etc.

Les CertusPro-NX continuent d’exploiter le process FD-SOI qui assure à cette famille une consommation réduite, jusqu’à quatre fois inférieure à celle des FPGA équivalents selon Lattice. L’Américain met également en avant leur temps de démarrage (configuration des entrées-sorties en 4ms et démarrage global en moins de 30ms) et la présence d’un moteur de cryptage AES-256 associé à l’authentification de bitstream ECDSA. Compatibles avec la dernière version de l’environnement de développement Lattice Radiant lancée pour l’occasion, les CertusPro-NX sont d’ores et déjà disponibles sous forme d’échantillons.