Pour son bloc d’IP USB SuperSpeed 3.0, Synopsys met à disposition des développeurs un des premiers modèles au niveau système de cette interface, conforme aux spécifications TLM 2.0 de l’OSCI. Face aux besoins de développer du logiciel embarqué le plus tôt possible dans le cycle de conception d’un SoC, Synopsys propose pour ses blocs d’IP USB SuperSpeed3.0 des modèles de haut niveau qui supportent les spécification de l’API TLM 2.0 (Transaction Level Models) décrite par l’Open SystemC Initative (OSCI). Écrits en SystemC, ces modèles sont notamment utilisables au sein de plateformes virtuelles qui autorisent l’écriture et le débogage de piles logicielles bien avant que le code RTL, et à fortiori les premiers prototypes matériels, soient disponibles.Ces modèles TLM, qui sont des représentations au niveau transactions de l’IP de l’interface USB 3.0 elle même et de l’IP du contrôleur Host xHCI (qui font partie de la bibliothèque DesignWare de Synopsys), fonctionnent sous n’importe quel simulateur SystemC conforme à la norme IEEE1666.

Dans la même rubrique

Le 20/12/2024 à 7:10 par Frédéric Rémond

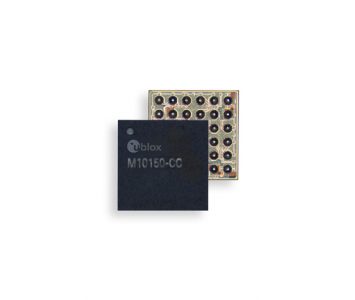

Les wearables et le positionnement satellite font bon ménage

Les wearables sont dans le collimateur de l'UBX-M1050-CC, le dernier circuit de positionnement par satellite d'u-blox. Ultra-compacte (2,39x2,39x0,55mm), la puce…

Le 10/12/2024 à 7:04 par Frédéric Rémond

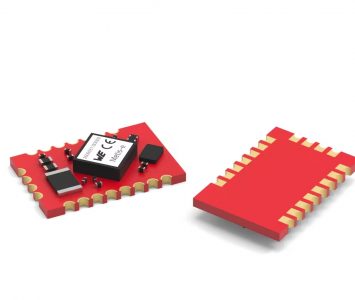

Les modules wM-Bus pour compteurs intelligents se miniaturisent

Les compteurs intelligents constituent le cœur de cible du Metis-e, le tout dernier module radio lancé par Würth Elektronik. Ce…

Le 09/12/2024 à 9:41 par Frédéric Rémond

Jusqu’à 6 W gérés par un convertisseur AC-DC secteur de 37x24x18 mm

En électronique de puissance comme ailleurs, combiner performances, fiabilité et prix doux n'est pas chose aisée. C'est pourtant l'objectif que…

Le 02/12/2024 à 9:30 par Frédéric Rémond

Des modules parés pour le Wi-Fi Sub-1 GHz à longue portée

Murata a enrichi son catalogue de deux modules de communication sans fil compatibles avec les standards Wi-Fi Sub-1 GHz (S1G),…