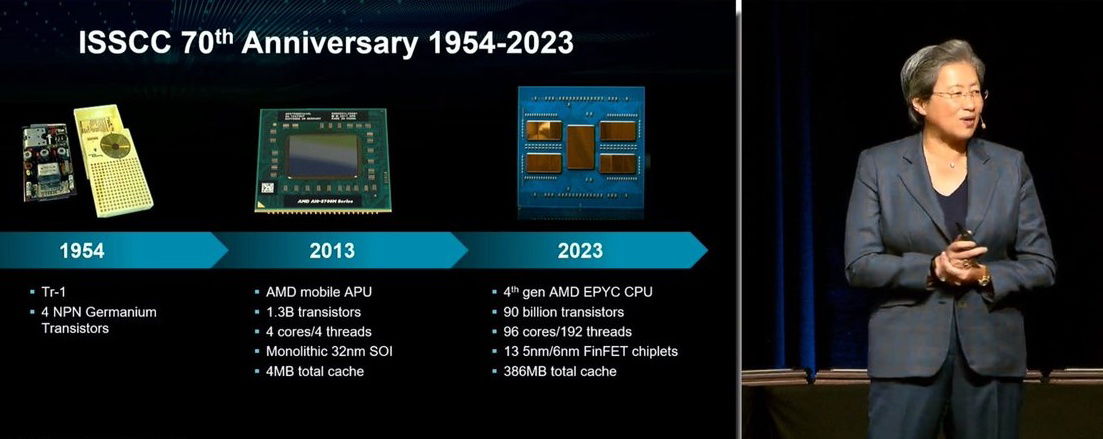

En préambule de la conférence ISSCC qui vient de fêter son soixante-dixième anniversaire à San Francisco, c’est la CEO d’AMD, Lisa Su, qui a eu l’honneur d’ouvrir les débats. Elle l’a fait avec une mise en garde : notre dépendance croissante à l’informatique à hautes performances ne sera pas soutenable d’un point de vue énergétique sans des progrès énormes concernant la consommation des puces impliquées. « Même si la loi de Moore a ralenti, les performances des supercalculateurs tendent à doubler toutes les 1,2 années, au moins deux fois plus vite que les progrès effectués en matière d’efficacité énergétique. A ce rythme, nous pourrions envisager des supercalculateurs de classe zettascale dans moins de dix ans, mais chacun nécessiterait une demie centrale nucléaire pour l’alimenter ! », explique Lisa Su. Ce qui n’est évidemment ni soutenable, ni souhaitable. Heureusement, des pistes existent pour maintenir la consommation des puces dans des limites plus raisonnables.

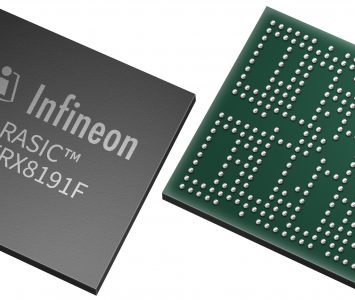

Le principal chantier, selon la CEO d’AMD, réside dans l’assemblage et l’encapsulation des circuits intégrés. Il n’est plus possible de compter seulement sur la réduction des géométries de gravure pour améliorer le rendement des circuits : les progrès ont ralenti dès le 7nm en termes de densité, et ont cessé à partir du 5nm en matière d’efficacité thermique. En outre, les coûts de production s’envolent pour les puces de grande taille produites dans les technologies de pointe. D’où l’avènement des architectures modulaires combinant de multiples chiplets rassemblés dans un même boîtier. Non seulement cette disposition permet d’optimiser le process pour chaque fonction (mémoire, traitement numérique, entrées-sorties, etc.), mais il rapproche physiquement les différents éléments ce qui rend les interconnexions beaucoup plus frugales.