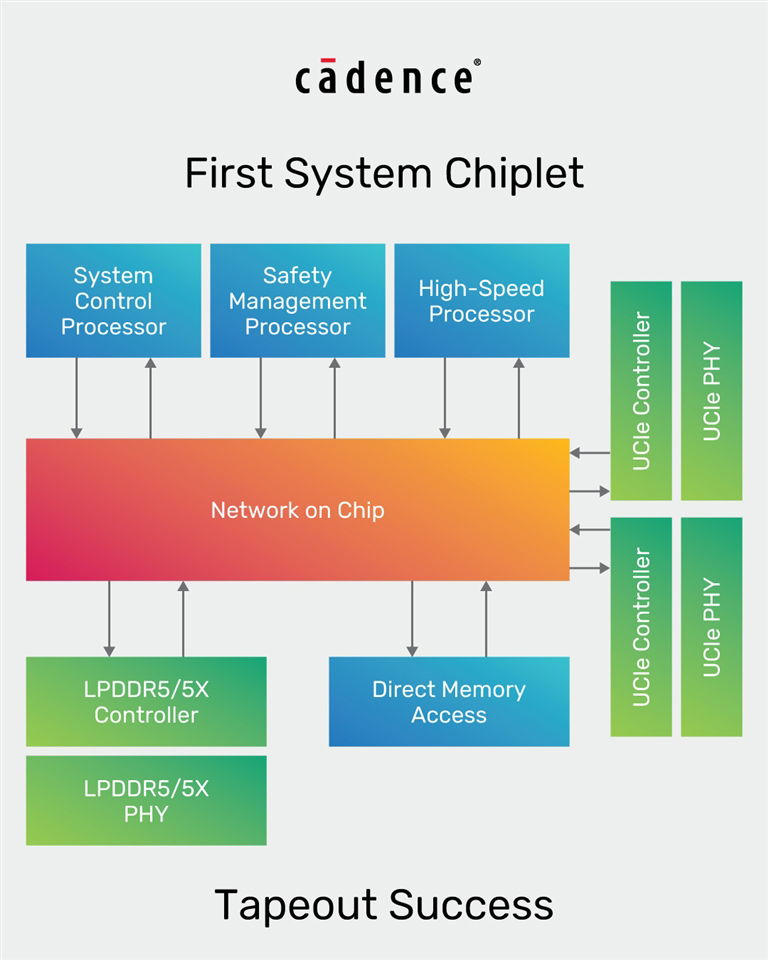

Comme beaucoup, Cadence mise sur les chiplets pour faire face à la complexité croissante des puces et augmenter leurs rendements de production. L’Américain vient ainsi de prototyper un composant mêlant des cœurs de traitement numérique (dédiés à l’application, à la gestion système et à la sûreté fonctionnelle), des contrôleurs mémoire LPDDR5/5X (y compris la couche PHY), un bloc d’accès mémoire direct et des interfaces compatibles UCIe (Universal Chiplet Interconnect Express). Le tout est relié à une matrice de connexion centrale Janus. Le composant répond à l’architecture CSA (Chiplet System Architecture) d’Arm et délivre jusqu’à 64Go/s côté UCIe et 32Go/s côté Dram.

Cadence prototype des circuits complexes à base de chiplets

© Cadence