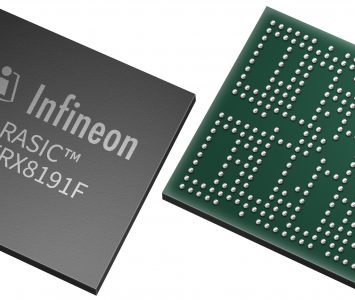

Confronté aux limites des mémoires flash embarquées à mesure que les géométries de gravure des microcontrôleurs s’affinent, NXP Semiconductors planche avec TSMC sur une mémoire magnétique Mram compatible avec le process FinFET 16nm du Taïwanais. Cette technologie est actuellement en cours de test, et les premiers échantillons commerciaux sont prévus début 2025 ; ils concernent des processeurs embarqués S32 dédiés à l’automobile.

Outre sa faculté à migrer dans des technologies plus fines, la mémoire Mram s’avère plus rapide que la flash. NXP note ainsi que la mise à jour de 20Mo de code ne prend que trois secondes en Mram, contre une minute en flash. L’endurance constitue l’autre avantage de la Mram, qui supporte typiquement un million de cycles de mise à jour, dix fois plus que la flash.