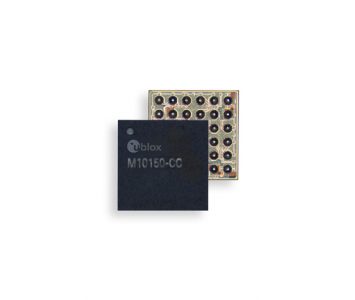

C’est une première dans l’industrie d’après Alphawave Semi. L’Anglais a mis au point un sous-système de transmission de données à 24Gbit/s en process 3nm, intégrable sous la forme d’un chiplet à interface UCIe (Universal Chiplet Interconnect Express). Cette IP utilise la technologie d’encapsulation CoWoS (Chip-on-Wafer-on-Substrate) 2.5D du fondeur taïwanais TSMC.

Le sous-système comprend les parties contrôle et gestion de couche physique (PHY), et supporte de multiples protocoles de transmission (PCIe, CXL, AXI-4, AXI-S, CXS, CHI…). Il cible les centres de données et les accélérateurs d’intelligence artificielle dotés d’une densité de bande passante de 8Tbit/s/mm.