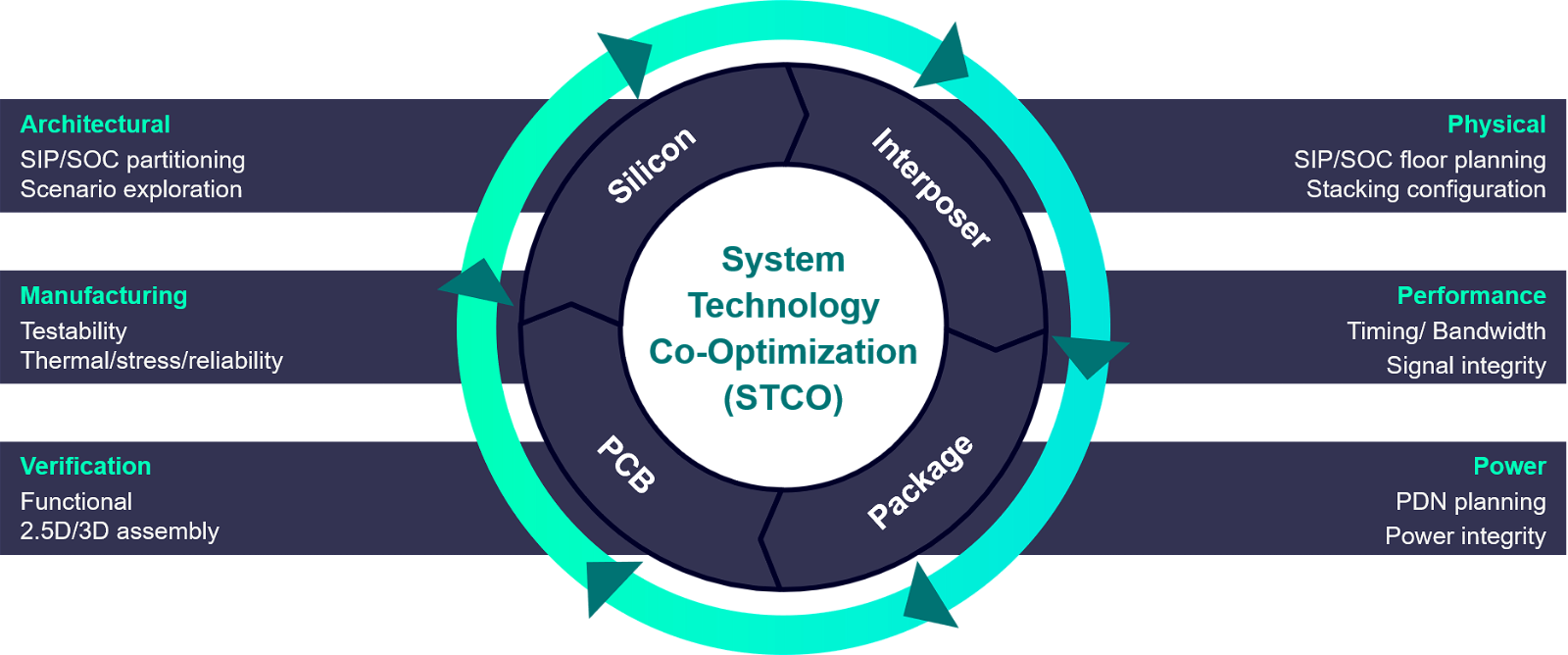

Puisque le modèle économique basé sur la réduction de la taille des transistors n’est plus universellement applicable, l’industrie électronique se tourne vers des technologies de packaging innovantes pour répondre aux exigences d’évolution des systèmes et réduire le coût de ces derniers. Cela a conduit à l’émergence d’une approche de co-optimisation de la technologie et des systèmes (STCO), dans laquelle un SoC est décomposé en modules plus petits (également appelés chiplets ) qui peuvent être conçus de manière concurrente par des équipes décentralisées, puis combinés en un système plus grand et extrêmement flexible à l’aide d’une méthode de conception de boîtier axée sur les chiplets , qui peut recourir au packaging 3D.

L’approche STCO offre de nombreux avantages, mais elle pose aussi de nouveaux défis. Elle permet aux équipes de conception décentralisées de travailler de manière à la fois simultanée et asynchrone. Cela signifie que différentes équipes peuvent travailler simultanément et indépendamment les unes des autres sur chaque fragment de la conception. Cela nous permet de choisir les processus optimaux pour chaque fragment.

Toutefois, pour ce faire, les données de tous les fragments doivent être réunies à un moment donné, et ce regroupement a lieu lors de la planification du boîtier. C’est lors de cette étape que nous réassemblons les blocs fonctionnels décomposés ( chiplets ) du SoC et que nous étudions les options de mise en boîtier.

Le partitionnement (décomposition) qui a été effectué aura un impact sur notre capacité à construire un boîtier fonctionnel et sur le coût de ce boîtier. La manière dont cette décomposition est effectuée a donc une grande importance, mais l’opération est généralement réalisée par des équipes qui auront besoin de prendre du recul et de s’outiller pour la suite du processus afin de prendre en compte l’impact de leurs décisions sur la mise en boîtier.

Le défi principal est le suivant : comment réintégrer les différents fragments de la conception dans un premier prototype de boîtier contenant suffisamment d’informations pour qu’il soit possible de procéder à une analyse multiphysique afin de mieux guider le partitionnement ? Cela implique d’évaluer la connectivité entre les chiplets. Cette analyse livre des informations essentielles. Une fois ces données retransmises à l’équipe chargée du silicium, celle-ci dispose d’informations précieuses pour reconsidérer le partitionnement, si cela s’avère nécessaire.

C’est dans ce cas de figure qu’une approche centrée sur l’anticipation ( shift-left ) est pertinente, et ceci afin d’effectuer l’analyse/simulation très tôt et d’utiliser ses résultats pour guider les décisions de conception et apporter des corrections afin de réduire le risque d’échecs lors des vérifications qui auront lieu plus tard dans le flux de conception. Cet article décrit pourquoi effectuer une telle analyse en amont dans les processus complexes de mise en boîtier pour des circuits avancés haute densité (HDAP) permet aux concepteurs de repérer très tôt les problèmes potentiels, et donc d’éviter d’intégrer des constructions défectueuses qui provoqueront des défaillances du CI et nécessiteront un travail de reconception important.

Guider le partitionnement grâce à une analyse en amont

Si le partitionnement était basé sur les blocs fonctionnels, la tâche serait facile. Les concepteurs pourraient prendre le schéma des blocs du circuit et faire de chaque bloc un fragment. Malheureusement, avec l’approche de STCO, ce n’est pas aussi simple.

Nous devons prendre en compte des éléments tels que les performances de chaque fragment et la manière dont il communique avec les autres fragments à un niveau plus détaillé. Par exemple, l’empilage 3D de puces va-t-il entraîner un gain de performance et de consommation ou, au contraire, causer un problème thermique ?

Nous cherchons à obtenir une solution plus performante et moins gourmande en énergie. Quelle que soit la méthode de partitionnement choisie, il existe toujours de nombreuses possibilités de décomposition et d’intégration ; trouver la bonne est la raison d’être de l’approche de STCO. Comme il existe probablement plusieurs bonnes solutions, pour déterminer quelle est la meilleure nous construisons un prototype de boîtier que nous utilisons pour analyser et évaluer chaque option de partitionnement intéressante.

Nous construisons ce prototype de manière incrémentale et nous l’affinons à mesure que les données deviennent plus précises (figure 1).

Figure 1. Version primitive d’un prototype de boîtier.

Au niveau du prototype de boîtier, nous sommes tout d’abord en mesure d’estimer l’intégrité de l’alimentation et des signaux ; le premier partitionnement retenu doit donc devenir un prototype de boîtier.

Comme son nom l’indique, le prototype de boîtier n’est qu’un modèle du boîtier envisagé, et non une implémentation détaillée. Nous connaissons la taille des blocs fonctionnels ( chiplets ) du circuit. Nous connaissons leurs signaux et, grâce à une description SystemVerilog du système, nous savons comment ils sont connectés entre eux. En utilisant un outil de visualisation Verilog, nous obtenons un aperçu clair du circuit, car il affiche une représentation graphique du code Verilog (figure 2).

Figure 2. Visualisation du code SystemVerilog sous forme graphique.

À ce stade, peut-être avons-nous des informations sur la matrice physique dans les descriptions LEF/DEF ; si c’est le cas, nous pouvons les utiliser pour créer un prototype plus détaillé.

Nous pouvons maintenant commencer par calculer le nombre de plots d’alimentation et de masse dont nous avons besoin pour chaque module et construire une carte des plots préliminaire. Nous disposons maintenant d’assez de données pour soumettre notre prototype de boîtier aux outils de vérification de l’intégrité de l’alimentation et effectuer une analyse préliminaire très en amont qui nous dira si tout semble correct ou si des problèmes existent (figure 3).

Figure 3. Simulation de l’intégrité de l’alimentation au niveau du prototype.

À ce stade, nous pouvons également effectuer une analyse préliminaire de l’intégrité des signaux et caractériser leurs E/S pour voir quelle configuration d’empilement 3D nous permet d’atteindre les performances escomptées et, surtout, d’anticiper les problèmes.

Pour résumer, nous faisons rentrer plus de silicium dans une surface plus petite en l’intégrant le long de l’axe Z : le volume. Il est évident que plus nous intégrons de silicium dans un petit volume, plus nous avons de risques de créer un problème thermique. Pour cette raison, une analyse thermique en amont est aussi vitale que l’analyse de l’intégrité des signaux et de l’alimentation. Comme nous n’en sommes qu’au début de la phase de conception, nous ne pouvons pas encore effectuer une simulation détaillée d’un domaine quelconque, mais là aussi nous pouvons aller assez loin avec ce que nous savons déjà. En effet, le prototype de boîtier nous donne la représentation physique, la conception du silicium nous donne une estimation de la puissance, et nous pouvons introduire ces informations dans un simulateur thermique 3D. 3D parce que ces boîtiers sont réellement des structures 3D, et que même s’il s’agit d’une estimation précoce, simplifier le boîtier en l’assimilant à une structure 2D serait trop trivial pour être utile (figure 4).

Figure 4. Prototypage thermique.

Nous avons étudié l’intégrité du signal, l’intégrité de l’alimentation et l’aspect thermique, mais comme nous disposons d’un modèle d’assemblage 3D complet (un jumeau numérique), nous pouvons, si nécessaire, étendre l’analyse aux contraintes mécaniques, aux déformations, aux défaillances de fixation de la puce, aux fissures du métal et à d’autres phénomènes physiques. L’intérêt de notre méthode c’est qu’elle nous permet d’utiliser le partitionnement de la propriété intellectuelle (PI) pour créer un prototype de boîtier, d’effectuer très tôt des simulations SI/PI et thermomécanique et d’utiliser les résultats pour ajuster le partitionnement.

Toutefois, l’analyse en amont ne remplace pas des simulations plus précises ou une vérification au niveau du boîtier et de l’assemblage ; et comme la complexité des systèmes s’accroît dans tous les domaines, une vérification finale en 3D de l’assemblage complet est le seul moyen de garantir la validité de la conception. Dans le cadre de la planification et du développement du modèle d’assemblage de boîtier 3D, nous définissons également le modèle de connectivité logique qui peut être utilisé pour piloter l’analyse prédictive, laquelle peut avoir lieu avant la conception physique (placement-routage) de l’assemblage de boîtier. Cela permet d’exécuter plusieurs cycles de vérification au cours du développement, ce qui aidera à identifier au plus tôt les problèmes susceptibles de retarder ou mettre en péril le projet s’ils étaient découverts au moment de la validation finale. L’anticipation est la clé pour développer une conception correcte par construction.

Comment s’assurer que le prototype de boîtier est correct ? En prenant le code Verilog du prototype de boîtier et en utilisant la simulation pour le comparer au code Verilog original.

Conclusion

Planifier à l’avance le partitionnement et l’intégration du système offre un avantage considérable pour l’implémentation physique, dans des domaines tels que l’intégrité de l’alimentation et du signal, les performances thermiques, la déformation du boîtier et les contraintes mécaniques. Par ailleurs, si le partitionnement et l’intégration ne sont pas gérés correctement, ils peuvent provoquer l’échec de l’ensemble du produit. Au cours du processus de partitionnement, il est souvent difficile de mesurer les conséquences sur les performances et la fiabilité du système. En effet, comme nous en sommes au début de la phase de conception, nous ne disposons pas d’informations suffisantes pour pouvoir effectuer des simulations détaillées précises, mais nous en savons assez pour effectuer des analyses rapides approximatives afin de détecter les problèmes.

Nous suggérons un processus où le partitionnement de l’ASIC est transmis très tôt au prototypage du boîtier, afin que les phénomènes physiques puissent être analysés. Les solutions issues du prototypage du boîtier, guidées par l’analyse multiphysique, sont renvoyées aux équipes chargées du silicium pour les aider à gérer le partitionnement de la PI et permettre aux équipes de conception de CI de prendre des décisions plus éclairées à un stade où le partitionnement peut encore être aisément modifié, c’est-à-dire avant que la conception ne soit trop avancée et que les coûts de résolution des problèmes ne deviennent prohibitifs. En d’autres termes, cela vous permet de prendre des décisions plus tôt.

Cette philosophie de l’anticipation, ou shift-left , s’appuie sur la solution HDAP (High Density Advanced Packaging) de Siemens EDA et les technologies Xpedition dédiées aux radiofréquences (RF) et aux hyperfréquences, qui font partie du portefeuille Xcelerator de Siemens Digital Industries Software. En adoptant cette philosophie et ces solutions, vos équipes seront en mesure de concevoir plus vite de meilleurs circuits, ce qui permettra à votre entreprise de créer dès aujourd’hui les innovations de demain.

Per Viklund est directeur de l’architecture des systèmes chez Siemens EDA. Dans ce poste, il est notamment responsable des technologies liées au développement de circuits RF et hyperfréquences et des solutions de packaging des circuits intégrés. Il possède plus de 40 ans d’expérience dans les domaines de la conception électronique et de l’EDA. Ces 30 dernières années, il s’est spécialisé dans l’EDA et s’est concentré sur les solutions dédiées pour le packaging des circuits avancés haute densité (HDAP) ainsi que la conception RF/hyperfréquences. Il a publié de nombreux articles sur les solutions de conception et d’analyse de circuits RF, le packaging des circuits intégrés et la conception conjointe de boîtiers de CI.