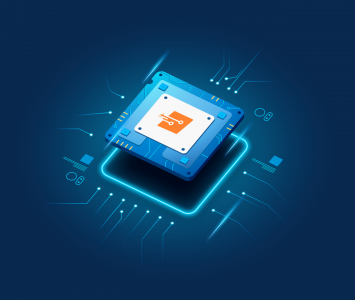

Les FPGA offrent une indéniable souplesse de développement et de conception au niveau matériel (ce qui les rend souvent préférables aux circuits spécifiques, qui doivent être reconçus de A à Z à chaque modification), mais leur exploitation logicielle demeure en retrait, en dépit des efforts constants des géants du secteur, Altera et Xilinx.

Cette difficulté devient encore plus aigue lorsqu’elle s’applique à des ingénieurs utilisant les FPGA comme des accélérateurs, et donc non rompus à toutes les subtilités de la conception sur circuits logiques programmables. C’est par exemple le cas dans les centres de données, un marché en pleine explosion et qui s’avère très gourmand en capacité de traitement mais aussi en souplesse d’utilisation tant les algorithmes et protocoles réseaux évoluent rapidement.

D’où la mise au point par Xilinx de SDAccel, un environnement de développement spécialement conçus pour les infrastructures réseaux et permettant de programmer ses FPGA en C/C++ ou en OpenCL, avec à la clé un rapport performances/consommation multiplié, selon la société, jusqu’à 25 par rapport aux microprocesseurs et processeurs graphiques utilisés pour ces applications, et jusqu’à 3 par rapport aux autres solutions FPGA du marché.

SDAccel relève d’une décennie d’étude et de développement interne à Xilinx et du rachat en 2011 d’AutoESL, spécialiste de la synthèse de haut niveau. Son compilateur s’adonne aux mêmes tâches qu’un compilateur OpenCL lambda, mais procure un niveau d’optimisation bien plus avancé (gestion de mémoires, flux de données, mise en pipeline ou en parallèle, etc.) qui, lorsque le code est porté sur un FPGA, renforce son efficacité jusqu’à tutoyer celle obtenue en RTL.

A découvrir dans le numéro de janvier de notre magazine “ElectroniqueS”.