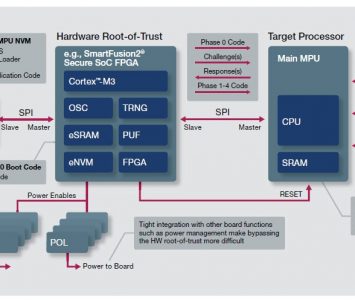

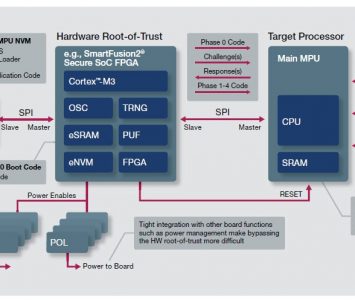

Microsemi sécurise l'initialisation des processeurs embarqués

L'américain utilise ses FPGA SmartFusion 2 pour sécuriser chaque étape d'initialisation d'un processeur embarqué. (suite…)

L'américain utilise ses FPGA SmartFusion 2 pour sécuriser chaque étape d'initialisation d'un processeur embarqué. (suite…)

Cadence lance une technologie héritée du rachat de Tensilica et permettant de décharger complètement le processeur hôte d'un système Android KitKat…

STMicroelectronics lance des microcontrôleurs combinant un coeur 32 bits Cortex M0+, un convertisseur analogique-numérique à faible consommation et une interface…

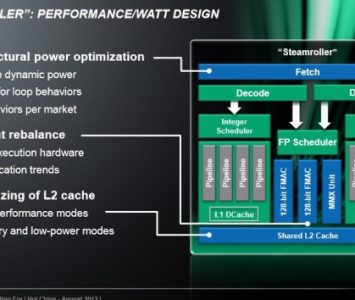

AMD a présenté les détails de l’architecture x86 64 bits double cœur Steamroller en Cmos planaire 28 nm, laquelle succèdera…

Analog Devices, a développé un CAN 14 bits 1 Géch./s offrant une marge dynamique de 86 dB. (suite…)

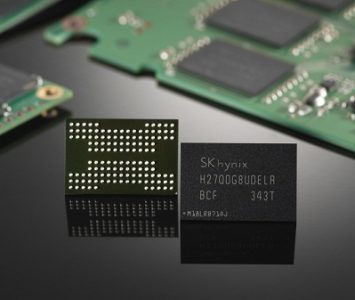

Micron et Hynix ont présenté des mémoires flash Nand MLC de 128 et 64 Gbits fabriquées en technologie Cmos planaire…

Réalisant la régulation de puissance côté primaire d'un pilote de LED, l'IRS2983 élimine un photocoupleur et d'autres composants. (suite…)

Samsung a développé une mémoire Dram DDR4 basse consommation de 8 Gbits fabriquée en Cmos 25 nm et délivrant jusqu’à…

Broadcom a développé un jeu de circuits 802.11ad en Cmos 40 nm capable de délivrer 4,6 Gbit/s à 10 mètres…

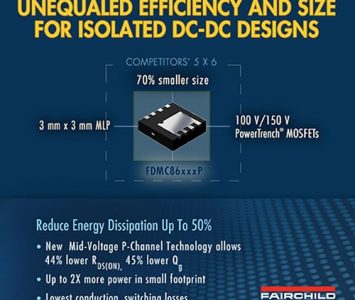

Proposés dans des petits boîtiers de 3 mm de côté, les FDMC86xxxP permettent de réduire la dissipation de puisance jusqu'à…

Samsung a présenté une mémoire Sram 6T basse consommation de 128 Mbits en technologie FinFET 14 nm. (suite…)

L'AD5683R cible un large éventail d'applications dans les domaines du contrôle de processus industriels, de l'instrumentation, du médical, des infrastructures…

L'américain a présenté à San Francisco Ivytown, un processeur Xeon à 15 cœurs 64 bits fabriqué en FinFET 22 nm.…