L'AMÉRICAIN EST LE PREMIER À FAIRE LA DEMONSTRATION DE CIRCUITS INTÉGRÉS GRAVES EN PROCESS 2 nm, GRÂCE À UNE TECHNOLOGIE À NANOFEUILLES PLUS PERFORMANTE, ET MINIATURISABLE, QUE LES TRANSISTORS FINFET ACTUELS.

L'AMÉRICAIN EST LE PREMIER À FAIRE LA DEMONSTRATION DE CIRCUITS INTÉGRÉS GRAVES EN PROCESS 2 nm, GRÂCE À UNE TECHNOLOGIE À NANOFEUILLES PLUS PERFORMANTE, ET MINIATURISABLE, QUE LES TRANSISTORS FINFET ACTUELS.

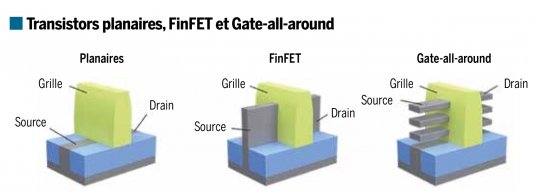

À mesure que les géométries se réduisent et donc que les électrons se font rares, les grilles tendent à enserrer le plus possible le chemin de conduction source-drain afin de mieux contrôler le transistor.

Contrairement à l'aileron des transistors FinFET, la largeur de ces trois nanofeuilles bles peut être optimisée pour modifier le compromis entre rapidité et consommation.

IBM ne produit plus guère de composants, mais reste une force qui compte dans le développement technologique pour circuits intégrés de pointe. L'Américain vient ainsi de présenter les premiers composants gravés en technologie 2 nm, là où l'état de l'art se situe à 5 nm en production et à 3 et 4 nm en R&D (prin-cipalement chez le fondeur taïwanais TSMC). Par rapport aux composants 7 nm actuels, cette technologie promet un gain de 45 % en performance à consommation égale ou de 75 % en consommation à performance égale selon IBM.

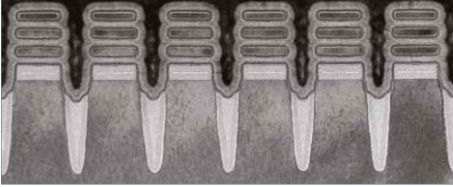

Ces développements ont été effectués dans le laboratoire Nanotech d'Albany, dans l'État de New York, où IBM travaille avec des partenaires publics et privés. La technologie 2 nm présentée ici repose sur une structure de transistor en nano-feuilles (nanosheets) à grille circulaire (Gate-all-around ou Gaa), contrairement aux transistors monoblocs FinFET Implémentation utilisés généralement en deçà de 10 nm. IBM avait déjà posé les bases de cette structure (qu'il étudie depuis une quin-zaine d'années) en 5 nm il y a trois ans avec ses partenaires Globalfoundries et Samsung, mais elle prend tout son sens ici car les transistors FinFET peinent à descendre à ce niveau de miniaturisation.

GATE-ALL-AROUND

Rappelons qu'à mesure que les géométries de gravure de semi-conducteurs rapetissent, les électrons circulant dans et le transistor la (gate) sont de moins en des structures moins nombreux de transistorset la commande du transistor de plus en plus délicate. Pour gagner en précision et limiter les fuites d'électrons, les grilles discrète de ces transistors « enserrent » donc de plus en plus le canal de conduction des électrons entre source et drain. Dans les transis-tors planaires classiques qui ont prévalus jusqu'à la génération 16/20 nm, la grille ne contrôle que le dessus du canal de conduction. Comme leur nom l'indique, les transistors FinFET sont formés d'un aileron (fin en anglais) vertical, la grille contrôlant ainsi trois côtés du canal de conduction des électrons. Les transistors de type GaaFET d'IBM, eux, sont constitués d'une grille entourant complètement le canal de conduction des électrons. Ce dernier est ici divisé en trois nanofeuilles de silicium empilées, chacune ne mesurant que quelques nanomètres d'épaisseur et étant entièrement cernée par la grille. En jouant Implémentation intégrée sur la largeur des nanofeuilles, il est ici possible de modifier le compromis entre rapidité et consommation, et de rendre ainsi une certaine flexibilité aux concepteurs, un transistor de mémoire n'ayant pas les mêmes besoins qu'un transistor de processeur par exemple.

IBM n'est bien sûr pas le seul à travailler sur cette nouvelle 8 canaux configurables structure de transistor. Parmi les grands centres de R&D en microélectronique, le CEA-Léti en France et l'Imec en Belgique planchent également sur le sujet, pour ne parler que des établissements européens. Parmi les fabricants, Intel développe sa propre mouture de transistor à nanofeuilles, appelées « nanoribbons » par l'Américain. Le fondeur taïwanais TSMC entend utiliser des transistors GaaFET, pour sa génération 2 nm, au plus tôt en 2023. Samsung devrait, lui, se mettre aux GaaFET dès la géométrie 3 nm, soit l'an prochain.