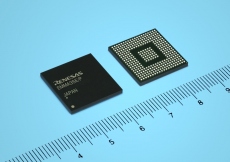

Le japonais passe ses processeurs pour boîtiers-décodeurs EMMA3 à la technologie 40 nm. Renesas Electronics lance l’EMMA3SE/P, un circuit de décodage TV destiné aux boîtiers-décodeurs. Il prend en charge la démodulation, la décompression et le traitement des images. Par rapport à son prédécesseur, l’EMMA3SE/P bénéficie d’une technologie de gravure plus fine (40 nm) et d’une interface DDR3 16 bits, ce qui lui permet d’être encapsulé dans un boîtier très compact de 17 x 17 mm.

Le japonais passe ses processeurs pour boîtiers-décodeurs EMMA3 à la technologie 40 nm. Renesas Electronics lance l’EMMA3SE/P, un circuit de décodage TV destiné aux boîtiers-décodeurs. Il prend en charge la démodulation, la décompression et le traitement des images. Par rapport à son prédécesseur, l’EMMA3SE/P bénéficie d’une technologie de gravure plus fine (40 nm) et d’une interface DDR3 16 bits, ce qui lui permet d’être encapsulé dans un boîtier très compact de 17 x 17 mm.

Outre les formats classiques (MPEG2, MPEG4, H.264, DivX, VC1, WMP…), il supporte le format H.264 MVC pour la diffusion d’émissions 3D et les standards VP6 et Sorenson Spark pour les émissions IP.