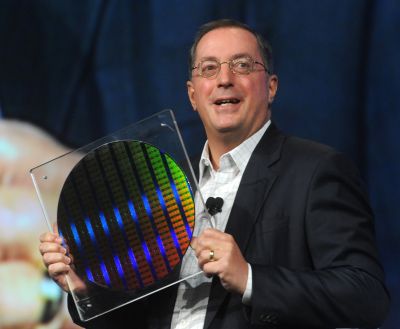

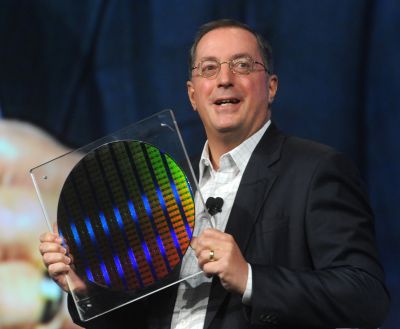

Intel a présenté en ouverture de son forum des développeurs un prototype de circuit intégrant près de 3 milliards de transistors en technologie 22 nm. En ouverture de son traditionnel forum des développeurs qui se tient cette semaine à San Francisco (Californie), Paul Otellini, p-dg d’Intel, a présenté une tranche de silicium comportant ce qu’il considère comme les premières puces opérationnelles en technologie 22 nm. Ces prototypes comportent tant de la mémoire Sram que les circuits logiques qui serviront aux futurs microprocesseurs du numéro un mondial des semiconducteurs.

Intel a présenté en ouverture de son forum des développeurs un prototype de circuit intégrant près de 3 milliards de transistors en technologie 22 nm. En ouverture de son traditionnel forum des développeurs qui se tient cette semaine à San Francisco (Californie), Paul Otellini, p-dg d’Intel, a présenté une tranche de silicium comportant ce qu’il considère comme les premières puces opérationnelles en technologie 22 nm. Ces prototypes comportent tant de la mémoire Sram que les circuits logiques qui serviront aux futurs microprocesseurs du numéro un mondial des semiconducteurs.

La tranche de silicium 22 nm qu’il a présentée se compose de matrices comportant 364 millions de bits de Sram et plus de 2,9 milliards de transistors. Ces puces renferment, selon M. Otellini, la plus petite cellule de mémoire Sram à être employée dans des circuits opérationnels, d’une superficie de 0,092 micromètre carré.

«Chez Intel, la loi de Moore se porte bien», a ainsi déclaré M. Otellini en précisant qu’en plus de ces prototypes 22nm, Intel a débuté la production de ses premiers processeurs en technologie 32 nm.

Ces processeurs connus sous le nom de code de Westmere, qui sont aussi les premiers à intégrer un cœur graphique, devraient être disponibles en production au quatrième trimestre.

Après le passage au 32 nm, Intel lancera une nouvelle microarchitecture, dont le nom de code est Sandy Bridge. Celle-ci se caractérisera par un cœur graphique de sixième génération placé sur la même matrice que le processeur et comportera des instructions vectorielles avancées ou AVX pour les calculs en virgule flottante, les contenus numériques et les logiciels qui sollicitent fortement le processeur.