Un nouveau flot logiciel réduit considérablement les délais de mise au point du silicium en réduisant l’ATE.

L’intelligence artificielle (IA) est actuellement l’un des principaux marchés pour les Circuits Intégrés. Les puces IA figurent également parmi les plus grandes et les plus complexes, avec des milliards de transistors, des milliers d’instances de mémoire et des implémentations DFT complexes avec des exigences uniques de mise au point (bring up) et de débogage. À ce stade, le volume de nouvelles puces IA est relativement faible, mais le délai de mise sur le marché revêt une importance capitale. Les équipes de conception doivent gagner du temps partout où elles le peuvent, et le processus de mise au point des modèles de test, de débogage et de caractérisation des circuits est doit être amélioré.

Après la fabrication, les vecteurs de test doivent être validés par rapport au silicium avant de procéder à l’intégralité du test de fabrication. En général, cela implique la conversion des vecteurs de test dans un format spécifique au testeur et la génération d’un programme de test qui sera exécuté par un équipement de test automatique (ATE). Lorsque l’un de ces vecteurs est en échec, la sortie ATE est ensuite traduite en données de défaillance de la puce et traitée par des outils de diagnostic. Cette méthode s’avère inefficace pour plusieurs raisons :

• Il faut passer du temps sur l’ATE, ce qui peut s’avérer coûteux et difficile à réserver

• Elle implique plusieurs équipes déconnectées : ingénieurs produits, ingénieurs DFT et équipe d’analyse des défaillances physiques

• Pour remonter des données de défaillance de la puce jusqu’au cœur du circuit, il manque souvent des informations de diagnostic

Ce flot standard de mise au point du silicium devient difficile à manier, mais il peut être considérablement amélioré en utilisant un logiciel EDA du commerce au lieu d’un ATE pour exécuter la séquence de test. Un système de type « desktop » réduit fortement le besoin d’un équipement de test coûteux dans le processus de mise au point des vecteurs de test, puisque tout le débogage et la caractérisation peuvent être effectués n’importe où. Il en résulte un cycle nettement réduit, une meilleure gestion des équipes interfonctionnelles et un diagnostic plus efficace des défaillances.

Le système « desktop »pour la mise au point du silicium est déjà utilisé avec succès par de grandes entreprises et des startups qui fabriquent des puces AI (comme Graphcore). Lors de l’International Test Conference (ITC) de 2018, la société Graphcore a expliqué comment elle a utilisé la solution de bureau de Mentor dans son papier intitulé « ATE Not Required: A Complete Test Solution to Accelerate First-Silicon Shipping of a Large AI Design. » Outre la mise au point du silicium, la société a utilisé le système « desktop » pour le test complet de ses pièces. Graphcore a terminé la mise au point du silicium en trois jours et a expédié des pièces entièrement testées et validées au cours de la première semaine, bien avant le délai prévu.

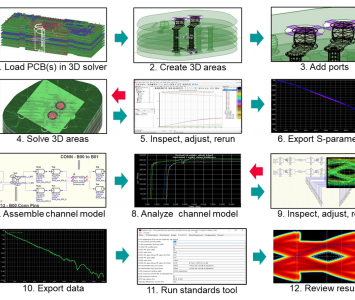

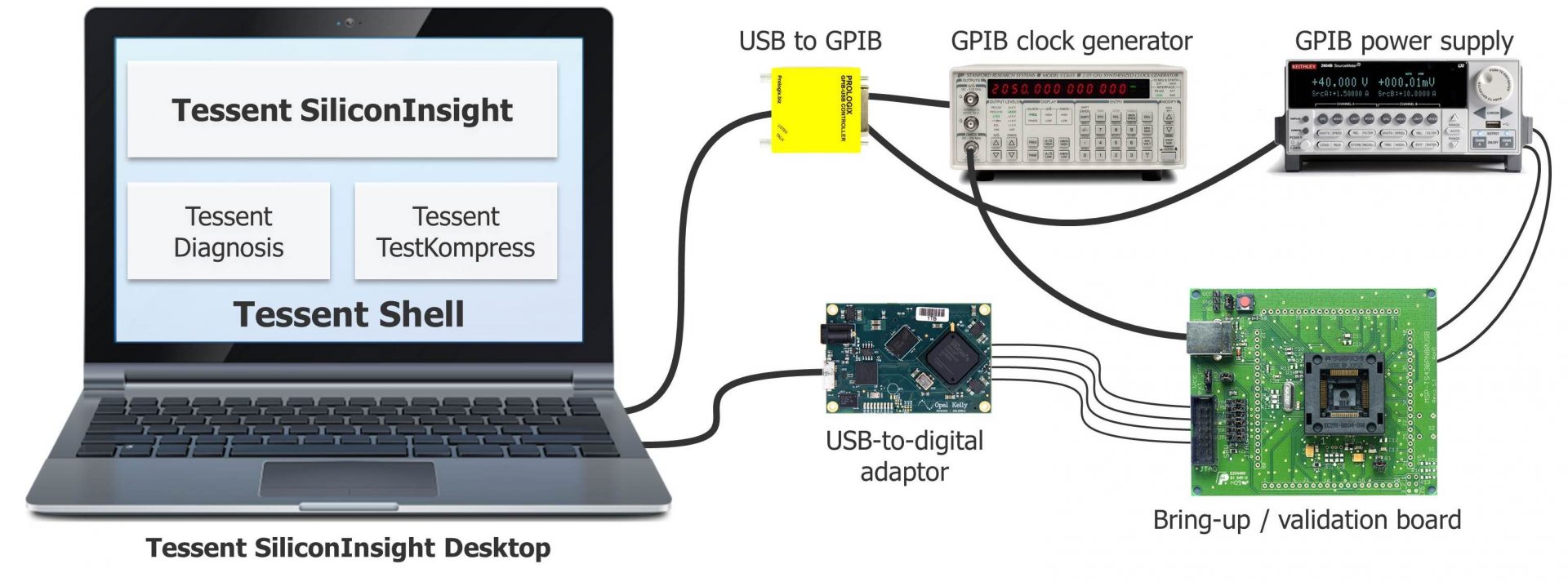

Le système « desktop » employé pour la mise au point du silicium (Figure 1) comprend un ordinateur équipé d’un adaptateur USB-numérique connecté à une carte de mise au point/validation avec le circuit en cours de test (DUT). Pour de nombreuses conceptions, une carte de validation est créée pour faciliter le développement de logiciels et d’autres applications de bring-up. La carte est essentiellement configurée pour émuler les conditions présentes pendant le test sur un ATE (telles que les broches d’alimentation, les horloges, les broches de configuration, etc.) et avec toutes les broches nécessaires au test disponibles pour l’adaptateur USB-numérique. Plusieurs adaptateurs différents peuvent être utilisés, en fonction du nombre de broches et de la tension d’E/S requise. Facultativement, des alimentations programmables GPIB et des générateurs d’horloge peuvent être utilisés pour automatiser la caractérisation du circuit.

Configuration d’un banc d’essai pour la mise au point du silicium. Ordinateur fonctionnant avec Tessent SiliconInsight, la carte de validation avec adaptateur USB, une alimentation et un générateur d’horloge.

Les configurations comparables disponibles dans le commerce se limitent aux BIST et à d’autres instruments de test accessibles exclusivement via le port JTAG du DUT. Ce nouveau système élargit le champ d’application aux tests non JTAG et à un éventail beaucoup plus large d’utilisation de vecteurs et de routines de diagnostic. Par exemple, les vecteurs ATPG avec compression et plus de 25 canaux de scan externe peuvent être testés et diagnostiqués par une simple action.

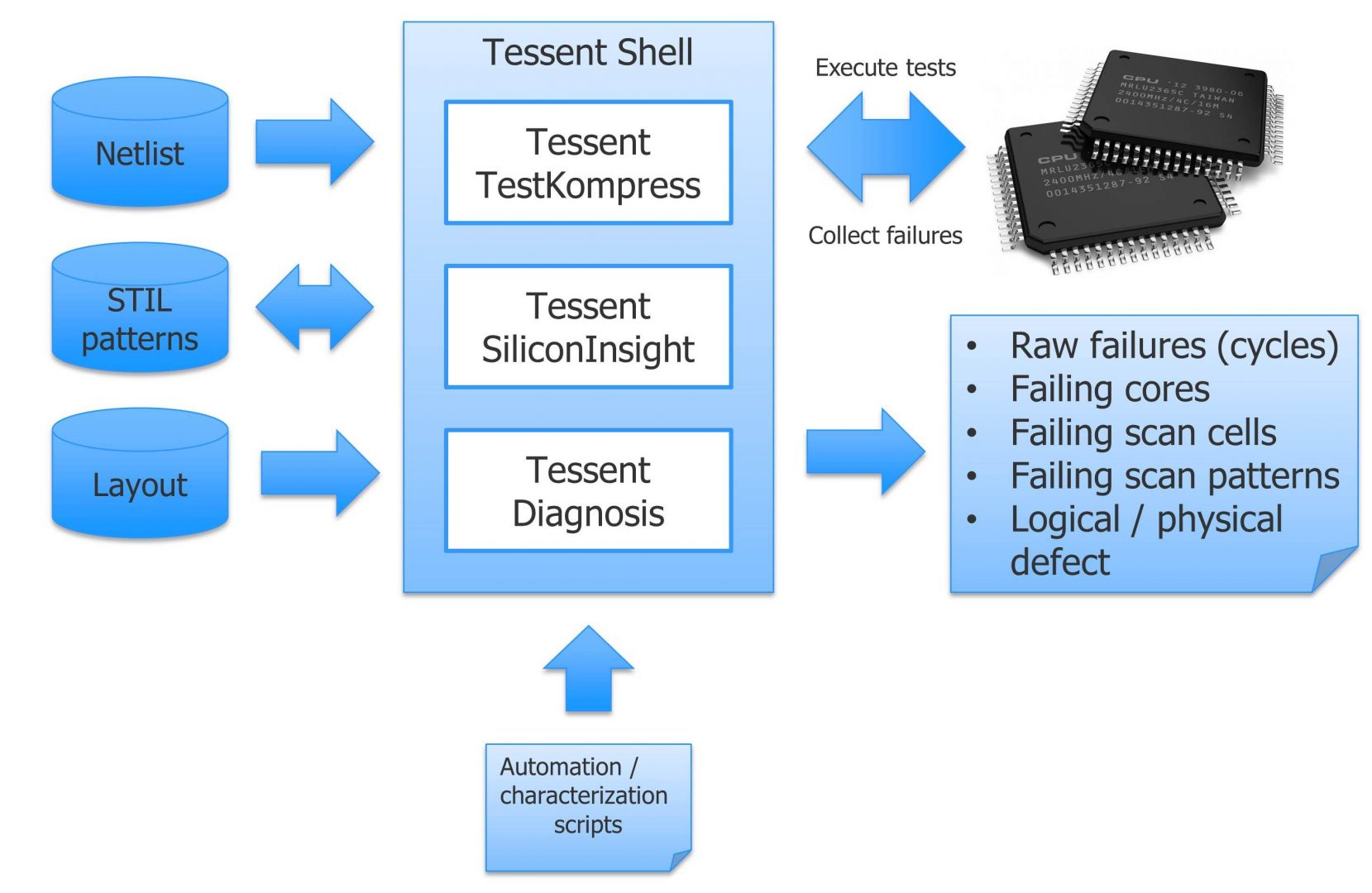

Le logiciel qui exécute les vecteurs de test, puis collecte et analyse les données de défaillance, est construit sur la même plate-forme logicielle DFT que celle utilisée pour créer les structures de test et générer les vecteurs. Cette plate-forme commune permet au logiciel de comprendre le fonctionnement de tous les protocoles et structures de test afin de fournir des résultats exploitables. Lorsque les vecteurs de test sont en erreur pendant la mise au point du silicium, on souhaite généralement déterminer quelles cellules de scan capturent les données défaillantes. En présence d’une compression du test et d’une DFT hiérarchique, un décodage complexe et des modèles de diagnostic spécifiques peuvent s’avérer nécessaires. Avec ce nouveau système, le mapping complexe et la génération de modèles de diagnostic associés est automatique et transparent à l’utilisateur, ce qui simplifie considérablement le processus de débogage. La figure 2 illustre le flot de mise au point du silicium.

Flot de mise au point du silicium dans un banc d’essai.

Autre caractéristique du processus de débogage : il peut inclure des informations de layout (sous la forme de fichiers LEF et DEF), ce qui facilite le processus de débogage en localisant le défaut dans le layout. La même méthode peut servir à la caractérisation du silicium, par exemple pour vérifier la variation de performances en fonction de la vitesse d’horloge et de la tension.

Pour les entreprises des segments hautement concurrentiels comme l’intelligence artificielle, il est important de gagner du temps dans le flot de conception de puces. L’utilisation d’un système « desktop » pour le bring-up, le débogage et le diagnostic des vecteurs de test peut réduire de 50 à 80 % la durée de cette phase, dans la recherche d’amélioration du processus de diagnostic des défaillances des CI. Le système « desktop » utilisé pour la mise au point des vecteurs de test accélère le débogage, la caractérisation et réduit la durée de cycle.

Auteur, Matthew Knowles, Product Marketing Manager chez Mentor, a Siemens Business.

https://www.mentor.com/products/silicon-yield/silicon-learning/