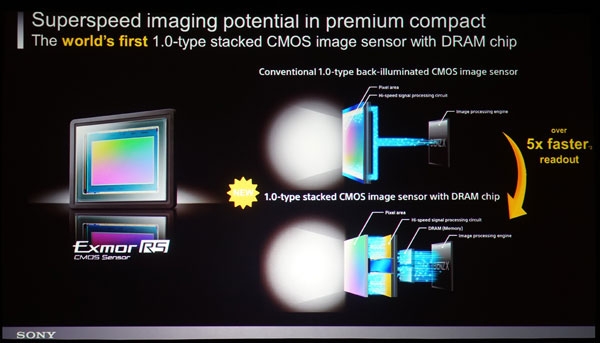

Le japonais insère une mémoire Dram de 1 Gbits entre l’imageur et le circuit de traitement du signal afin d’offrir des fonctions inédites.

San Francisco – Sony a présenté à la conférence ISSCC un capteur d’images Cmos à vingt millions de pixels qui se démarque par sa structure. On sait le Japonais à la pointe des imageurs dits empilés, où la puce du capteur surplombe au moyen de vias traversantes une autre puce chargée du traitement du signal et fabriquée dans un process différent. Le capteur présenté à San Francisco va plus loin : il comprend un processeur en Cmos 40nm, une mémoire Dram de 1Gbits en Cmos 30nm et un imageur en Cmos 90nm. L’objectif est d’utiliser la mémoire Dram pour bénéficier à plein de la capacité de capture rapide de l’imageur, jusqu’ici freiné par la relative lenteur des échanges de données. Cela permet d’implémenter des fonctions originales, comme la capture vidéo au ralenti ou l’incrustation d’images en mode vidéo, et également de limiter la distorsion induite par la lecture en balayage du capteur – ces imageurs destinés aux smartphones ne pouvant bénéficier d’un obturateur mécanique comme ceux des appareils reflex. Typiquement, à pleine définition, le capteur peut transférer dix images à la Dram dans le temps habituellement imparti pour en envoyer une seule au circuit de traitement. En mode vidéo Full-HD à 30 images/seconde, il peut émettre jusqu’à 960 images pour, par exemple, rendre compte d’un mouvement brusque. Ces données supplémentaires sont assignées à un canal virtuel distinct sur l’interface MIPI.

Au sein du module, les données émises par les photosites sont numérisées via des convertisseurs analogique-numérique 10 bits, puis soumises à un prétraitement (compensation de niveau de noir, gain numérique…) et véhiculées sur un bus 512 bits capable de manier jusqu’à 102Gbit/s. Selon les besoins de l’application, à partir de ce bus, elles ont alors accès à la mémoire Dram, au bloc de traitement principal (correction de défauts, réduction de bruit, mise à l’échelle, etc.) et à la sortie MIPI.