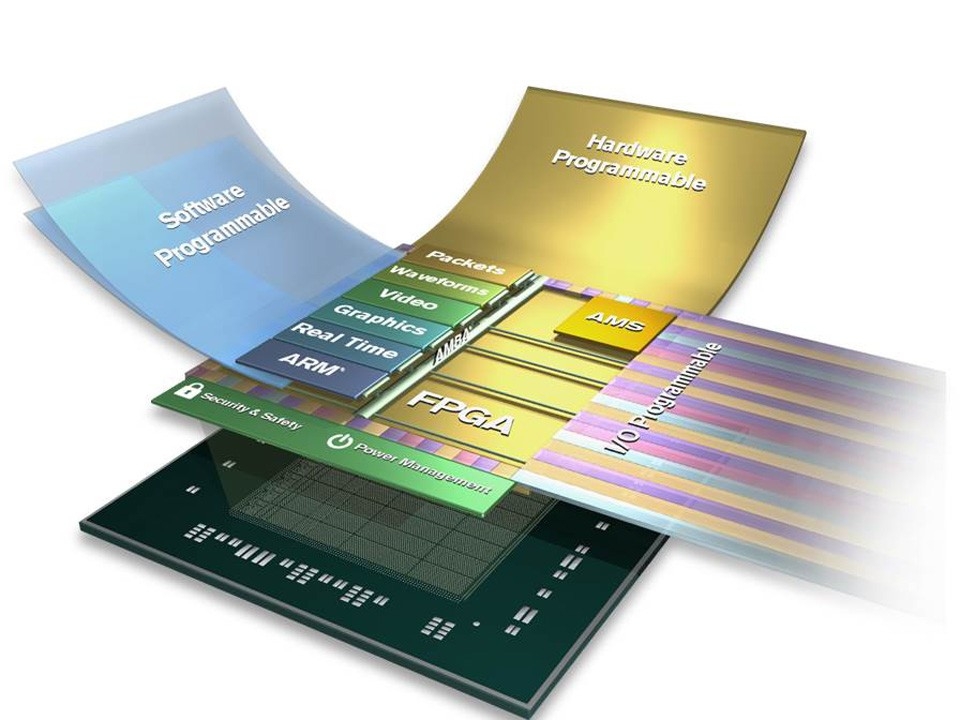

Xilinx vient d'annoncer l'échantillonnage de ses FPGA UltraScale+ pour la fin de l'année 2015 avec, dès le second trimestre, un accès restreint aux outils de conception et aux premiers prototypes.

Comprenant des mises à jour des familles Kintex, Virtex et Zynq, ces UlstraScale+ bénéficient en premier lieu d'une nouvelle architecture mémoire basée sur des blocs dits UltraRAM huit fois plus gros que les traditionnels blocs de Ram utilisés jusqu'ici. Ils offrent en outre des performances et une latence pré-visibles, et peuvent être étendus jusqu'à une capacité de 432 Mbits.

Deuxième innovation des UltraScale+ : la technologie SmartConnect, qui comme son nom l'indique permet d'optimiser en bande passante et en latence les interconnexions entre les différentes parties de la puce avec, à la clé, un gain de 20 à 30% en termes de surface de silicium, de performances et de puissance consommée selon Xilinx. Elle facilite pour cela l'arbitrage entre différentes méthodes de liaison de blocs de propriété intellectuelle afin de choisir dans chaque cas celle qui convient le mieux à l'application (mise en paquets, matrice, cellules d'arbitrage, connexion directe, etc.).

Enfin, les systèmes sur une puce Zynq UltraScale+ tireront profit d'architectures hétérogènes mettant en scène des cœurs 64 bits Cortex-A53 (remplaçant les précédents Cortex-A9) pour les tâches lourdes et des Cortex-R5 pour le traitement en temps réel, ainsi que des moteurs graphiques Mali-400MP.

A découvrir dans le numéro de mars de notre magazine "ElectroniqueS".