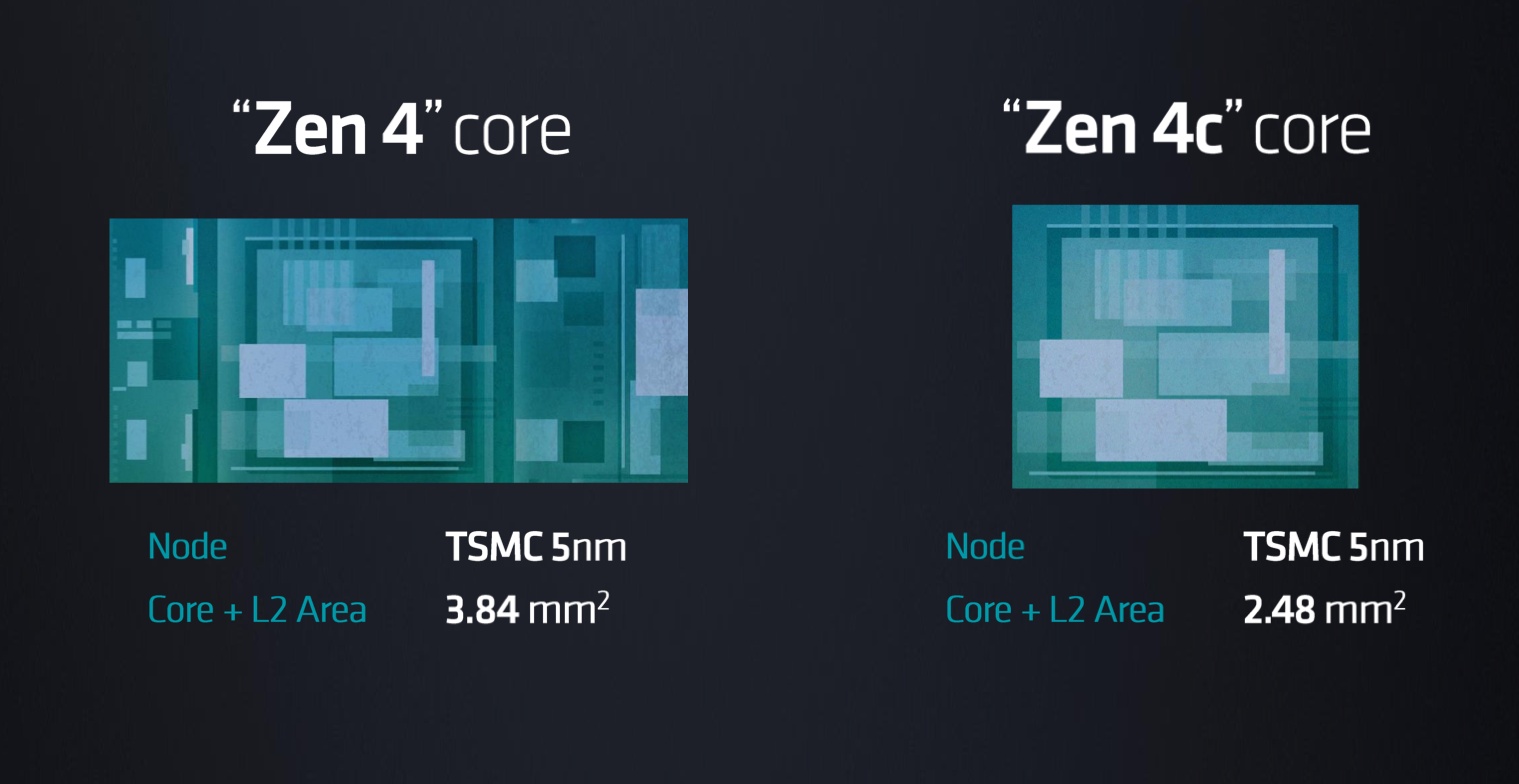

AMD a profité de la conférence ISSCC pour décrire son cœur Zen 4c, qui tient une place à part dans son catalogue. Il s’agit en effet de la première déclinaison de cœur Zen optimisée en surface et en consommation, visant tout particulièrement les applications embarquant un grand nombre de cœurs comme les serveurs. Décliner un cœur de base en versions optimisées pour la puissance de calcul ou pour le rendement énergétique n’est pas nouveau : c’est un principe utilisé de longue date dans les architectures Arm, et repris depuis quelques temps par Intel au sein de ses processeurs mêlant des cœurs estampillés P (Performance) et E (Efficient). La différence est que le Zen 4c d’AMD reprend exactement la même architecture et le même jeu d’instructions que le Zen 4, ce qui lui permet de se passer d’un organisateur (scheduler) OS matériel pour orchestrer le tout, de simplifier le traitement multitâche et d’obtenir un comportement plus prévisible sans ajout d’instructions. Pourtant, l’Américain annonce, pour un même process TSMC 5nm, une réduction de 35% de la surface de silicium occupée et des gains respectifs de 25% et 9% en performances/mm² et performances/W.

D’où viennent ces améliorations ? En premier lieu, de la mémoire embarquée. Le cache de niveau 3 a ici été réduit de 4 à 2Mbits par cœur. En outre, la Sram embarquée a été optimisée : là où les Zen 4 employait ces cellules de mémoire à huit transistors, les Zen 4c ont recours à des cellules à six transistors seulement. A l’échelle de la puce, cette optimisation permet de réduire la taille de plus de 35%. Avec des cœurs Zen 4C plus compacts, et ainsi plus nombreux à surface de silicium équivalente, les processeurs qui en sont équipés seraient également, d’après AMD, plus aptes à gérer les algorithmes d’intelligence artificielle gourmands en parallélisme. Ce que l’Américain entend prouver, bancs d’essai à l’appui, face au Xeon 8490H d’Intel et à l’Altra Max M128-30 d’Ampere.