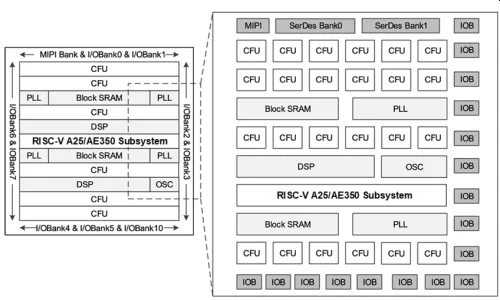

Encore mal connu en Occident, le Chinois Gowin Semiconductor a été fondé en 2014 avec comme objectif de combler le manque local de savoir-faire en logique programmable, et propose désormais toute une gamme de FPGA à cellules Sram ou flash. Et il vient de s’associer à Andes Technology pour incorporer des cœurs RISC-V de ce dernier, à savoir l’AndesCore A25 et le sous-système périphérique associé AE350, au sein de ses FPGA GW5AST-138. D’après les deux sociétés, c’est la première fois qu’un cœur RISC-V trouve sa place dans un FPGA gravé en 22nm – en attendant sans doute que Microchip mette à jour ses PolarFire.

L’AndesCore A25 est cadencé jusqu’à 400MHz et inclut les extensions RISC-V relatives aux instructions DSP/SIMD, à la manipulation de bits et au calcul en virgule flottante en précision simple et double, ainsi qu’à la gestion de mémoire MMU. Au-delà des blocs déjà fixés en hardware (Serdes, agrégation vidéo, accélération IA, Ram à correction ECC, horloges, etc.), le réseau logique à 138K tables LUT du FPGA permet d’ajouter les autres fonctions nécessaires à l’application.