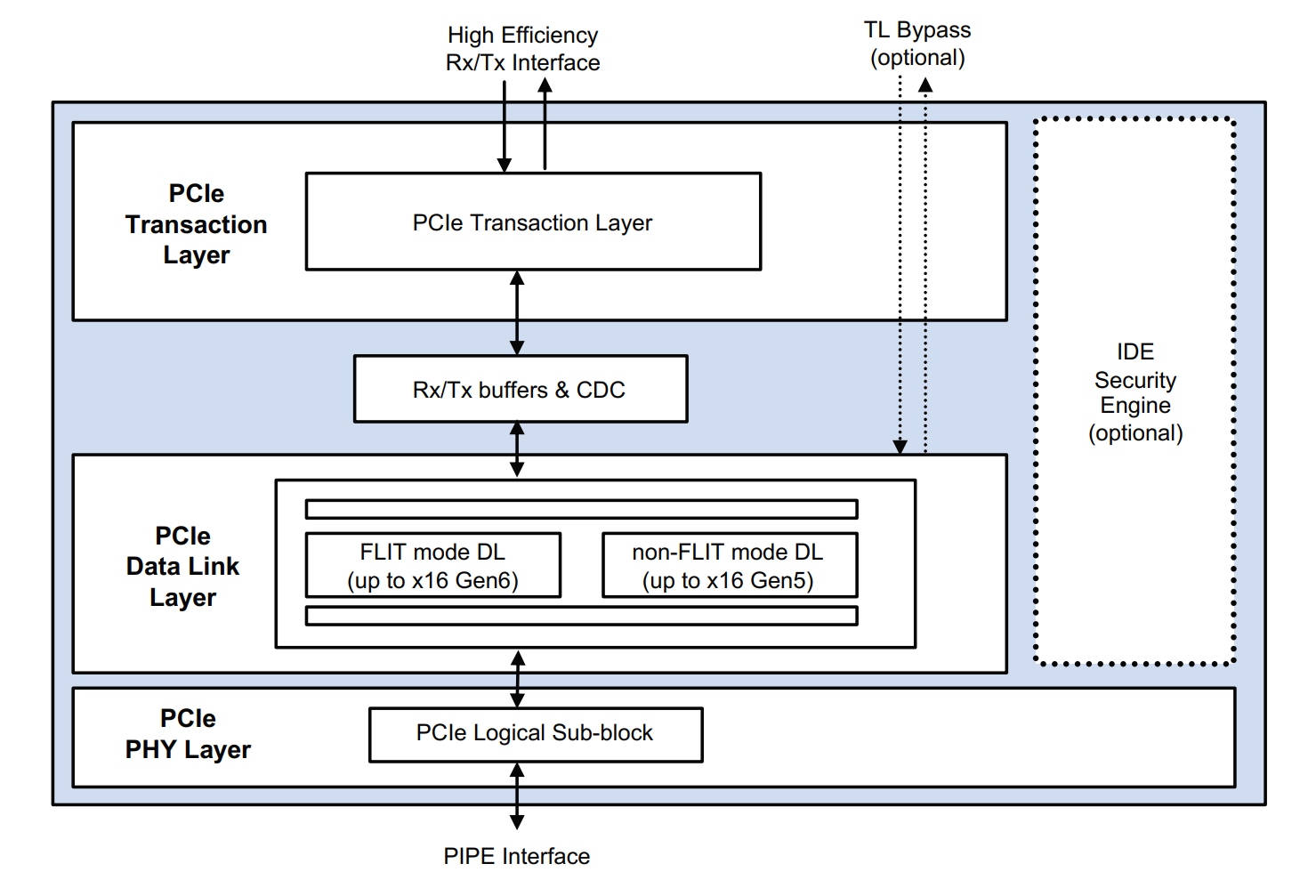

A peine finalisée, la spécification PCIe 6.0 fait déjà l’objet d’un contrôleur sous forme de bloc d’IP chez Rambus. Ce contrôleur assure 64 Gtransferts/s en modulation PAM4 et comprend en option un moteur de cryptage IDE (integrity and data encryption) protégeant la liaison PCIe contre les attaques physiques. Sont visés dans un premier temps les FPGA et circuits spécifiques pour centres de données et calculateurs IA.

Le PCIe 6.0 déjà disponible chez Rambus