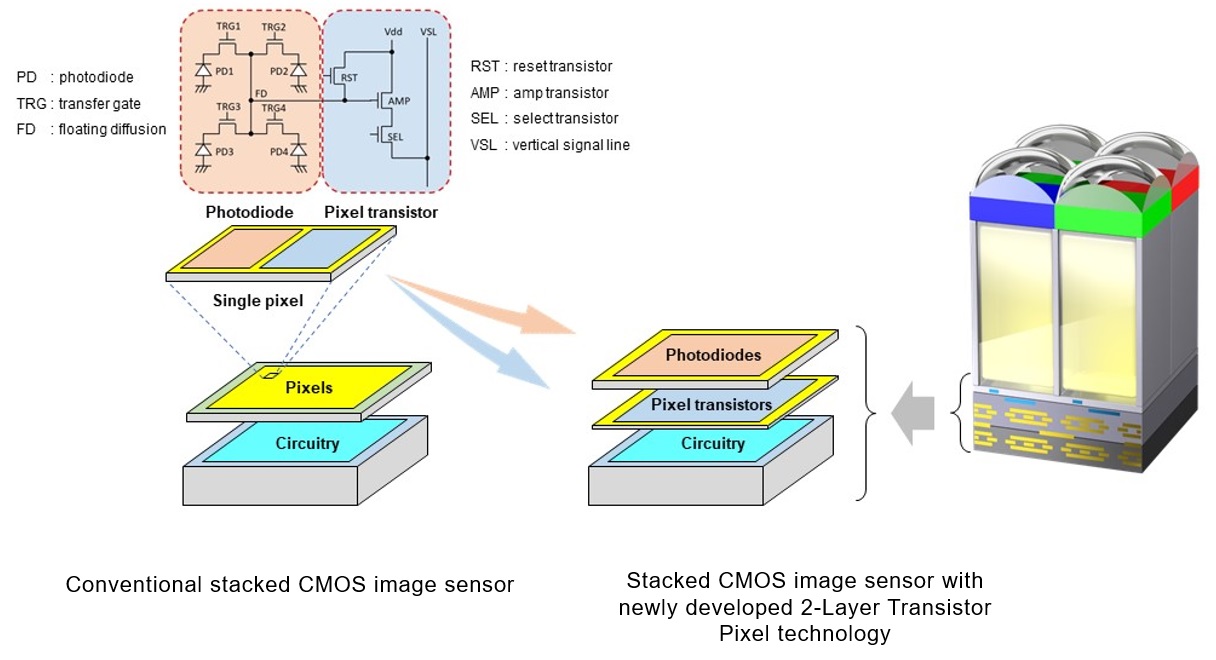

Lors de la dernière conférence IEDM, Sony a exposé une architecture novatrice d’imageur Cmos dotée de pixels à deux couches et, par conséquent, d’une dynamique supérieure.

D’ordinaire, chaque photosite d’un imageur héberge côte à côte la photodiode elle-même et les transistors chargés de son contrôle. Grâce à une technique propriétaire d’empilement, Sony a réussi ici à superposer une couche ne contenant que les photodiodes au-dessus d’une couche dévolue aux transistors de commande – le tout étant empilé au-dessus d’un circuit de traitement du signal comme chez les précédents imageurs dits stacked du Japonais. Chacune de ces deux couches peut dès lors être optimisée, avec comme effet principal le doublement du niveau de saturation des photodiodes. Disposant eux aussi de davantage d’espace, les transistors de contrôle en général et surtout ceux dévolus à l’amplification ont vu leur taille croître, ce qui a permis au fabricant de diminuer leur niveau de bruit et donc les performances de l’imageur en environnement sombre. Sony entend appliquer cette nouvelle architecture aux capteurs destinés aux smartphones.